VDD2

VDDS

SDMMC1_VDDS

/ SIM_VDDS

PWRDNZ

X

scm-021

Public Version

www.ti.com

SCM Programming Model

Table 13-68. PBIAS Error Signal Truth Table (continued)

VMODE

PWRDNZ

SUPPLY_HIGH

PBIAS ERROR

X

1

X

1

1

0

X

0

1

1

0

1

1

1

1

0

NOTE:

PBIAS ERROR = 1: VMODE level not same as SUPPLY_HIGH

PBIAS ERROR = 0: VMODE level same or VMODE not considered

The PBIAS errors, PBIAS0_ERROR and PBIAS_ERROR1, are merged and connected to the MPU

subsystem interrupt controller.

The CONTROL.

[i] PBIASLITEVMODEERROR (where i = 3 or 11) bits also

indicate if this kind of error occurs.

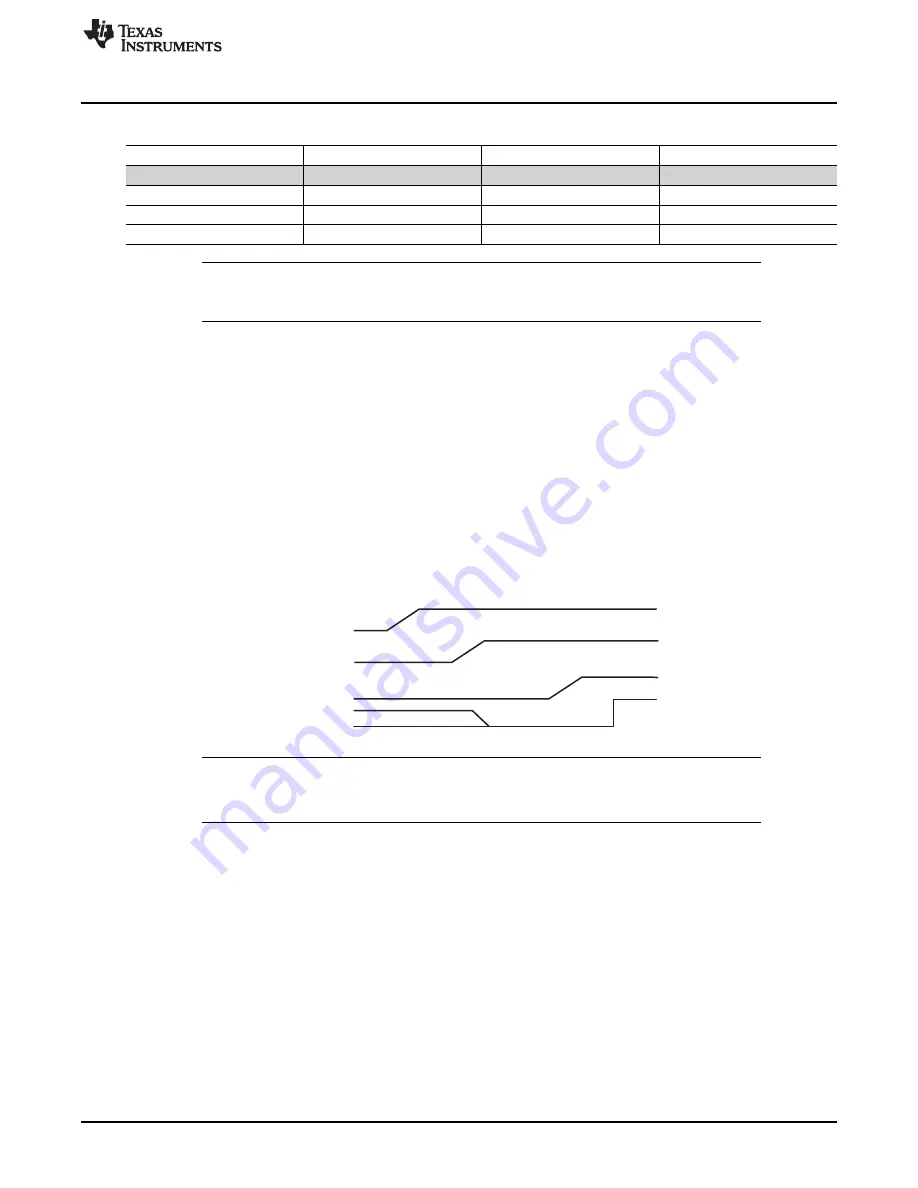

13.5.2.2 Critical Timing Requirements

It is crucial that the PBIAS and I/O cell related PWRDNZ bits are deasserted (made 1 from 0) only after

SDMMC1_VDDS/SIM_VDDS is stable. The device supports only the power-up sequence in which VDD2

ramps up before VDDS. However, SDMMC1_VDDS/SIM_VDDS must come up after both VDD2 and

VDDS.

show the expected behavior of PWRNDZ bit with regard to supply ramp up. This figure also

shows the only possible combination when VDDS ramps up before VDD2.

Figure 13-25. VDDS Ramps Up Before VDD2

NOTE:

These timing requirements are applicable only when SDMMC1_VDDS/SIM_VDDS is 3.0 V.

If SDMMC1_VDDS/SIM_VDDS is 1.8 V, VDDS and SDMMC1_VDDS/SIM_VDDS can be

ramped up simultaneously.

13.5.2.3 Speed Control and Voltage Supply State

There are other control bits, PRG_SDMMC1_SPEEDCTRL in the CONTROL.

and

SUPPLYHIGH in the CONTROL.

registers:

•

PRG_SDMMC1_SPEEDCTRL bit can be used to reduce dynamic current if fast rise/fall times are not

needed.

•

SUPPLYHIGH bit signal is used to inform the cell on the value of SDMMC1_VDDS/SIM_VDDS signal

(0b0 = 1.8 V and 0b1 = 3.0 V).

13.5.3 Off Mode Preliminary Settings

The following actions must be performed once, and remain valid for all device OFF <-> ON transitions:

2539

SWPU177N – December 2009 – Revised November 2010

System Control Module

Copyright © 2009–2010, Texas Instruments Incorporated

Содержание OMAP36 Series

Страница 174: ...174 List of Tables SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 692: ...692 MPU Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1084: ...1084 IVA2 2 Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1990: ...1990 2D 3D Graphics Accelerator SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2334: ...2334 Memory Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2700: ...2700 Memory Management Units SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2868: ...2868 HDQ 1 Wire SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2974: ...2974 UART IrDA CIR SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3054: ...3054 Multichannel SPI SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3462: ...3462 MMC SD SDIO Card Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3508: ...3508 General Purpose Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3584: ...3584 Initialization SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3648: ...3648 Debug and Emulation SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...