GPMC_FCLK

GPMC_CLK

WAIT

Valid Address

Valid Address

Data

CSONTIME

CSWROFFTIME

ADVONTIME

ADVWROFFTIME

WEONTIME

WRDATAONADMUXBUS

WEOFFTIME

WRCYCLETIME

nBE1/nBE0

nCS

nADV

nWE

gpmc_a[11:1]

gpmc_d[15:0]

(connected to A[26:17] on

memory side)

(connected to A[16:1] /D[15:0] on

memory side)

gpmc-013

Public Version

www.ti.com

General-Purpose Memory Controller

•

The end of the access is defined by the WRCYCLETIME parameter.

This write-cycle time is defined in the GPMC.

[12:8] WRCYCLETIME field.

After a write operation, if no other access (read or write) is pending, the data bus keeps its previous value.

See

, Bus Keeping Support.

In the GPMC, when a 16-bit wide device is attached to the controller, a Word32 write access is split into

two Word16 write accesses. For more information about GPMC access size and type adaptation, see

, System Burst Versus External Device Burst Support.

Between two successive accesses, if an nCS pulse is needed:

•

The GPMC.

[11:8] CYCLE2CYCLEDELAY field can be programmed with

GPMC.

[7] CYCLE2CYCLESAMECSEN enabled.

•

The CSWROFFTIME and CSONTIME parameters also allow a chip-select pulse, but this affects all

other types of access.

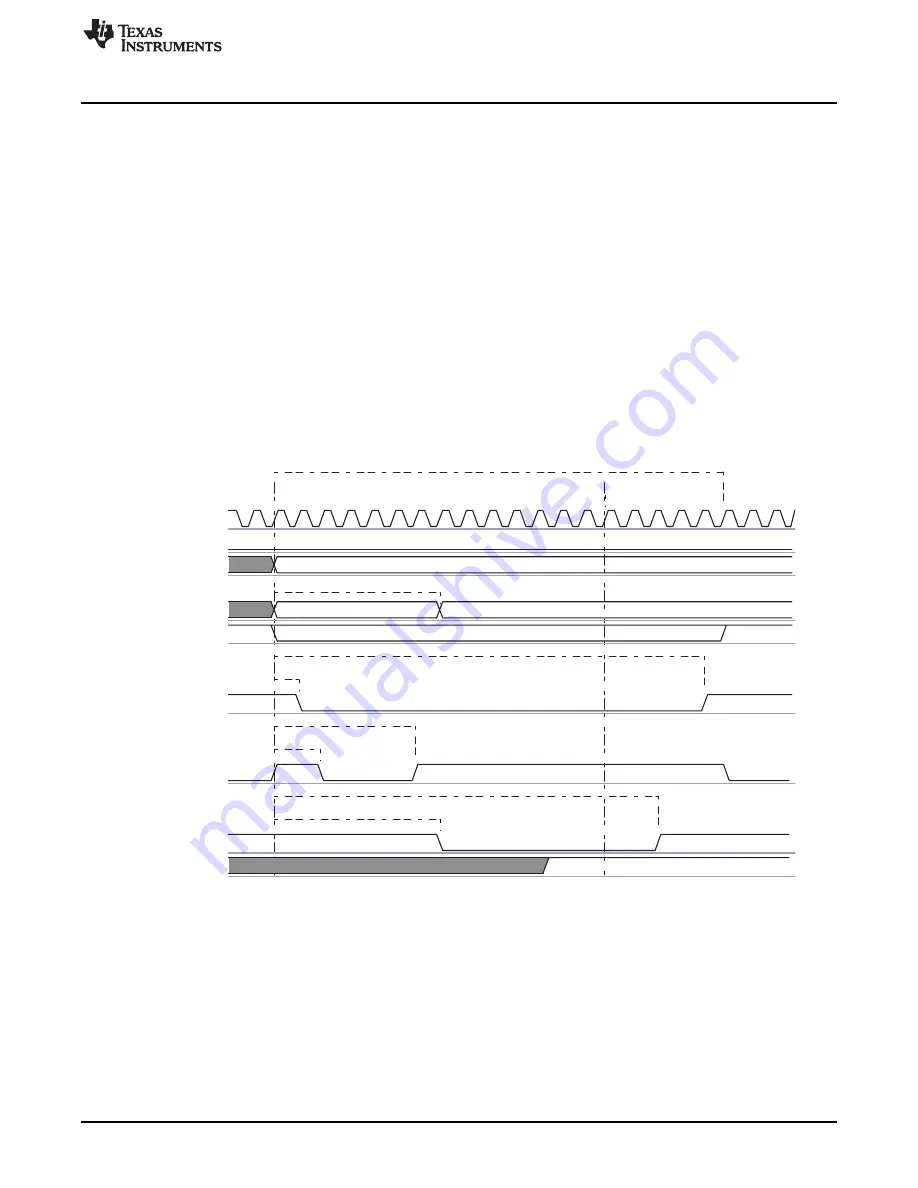

10.1.5.9.2.2 Asynchronous Single Write Operation on an Address/Data-Multiplexed Device

shows an asynchronous single write operation on an address/data-multiplexed device.

Figure 10-13. Asynchronous Single Write on an Address/Data-Multiplexed Device

When the GPMC generates a write access to an address/data-multiplexed device, it drives the address on

the address/data muxed bus until WRDATAONADMUXBUS time, and then it drives the data. For more

information, see

, Address/Data-Multiplexing Interface.

register settings (i = 0 to 7):

•

WRITEMULTIPLE bit at 0 (write single access)

•

WRITETYPE bit at 0 (write asynchronous)

•

MUXADDDATA bit at 1 (address/data-multiplexed device)

Address bits [16:1] are placed on the address/data bus at the start of cycle time, and the remaining

address bits [26:17] are placed on the address bus.

The nCS, nADV, and nWE signals are controlled in the same way as nonmultiplexed accesses.

2145

SWPU177N – December 2009 – Revised November 2010

Memory Subsystem

Copyright © 2009–2010, Texas Instruments Incorporated

Содержание OMAP36 Series

Страница 174: ...174 List of Tables SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 692: ...692 MPU Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1084: ...1084 IVA2 2 Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1990: ...1990 2D 3D Graphics Accelerator SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2334: ...2334 Memory Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2700: ...2700 Memory Management Units SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2868: ...2868 HDQ 1 Wire SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2974: ...2974 UART IrDA CIR SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3054: ...3054 Multichannel SPI SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3462: ...3462 MMC SD SDIO Card Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3508: ...3508 General Purpose Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3584: ...3584 Initialization SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3648: ...3648 Debug and Emulation SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...