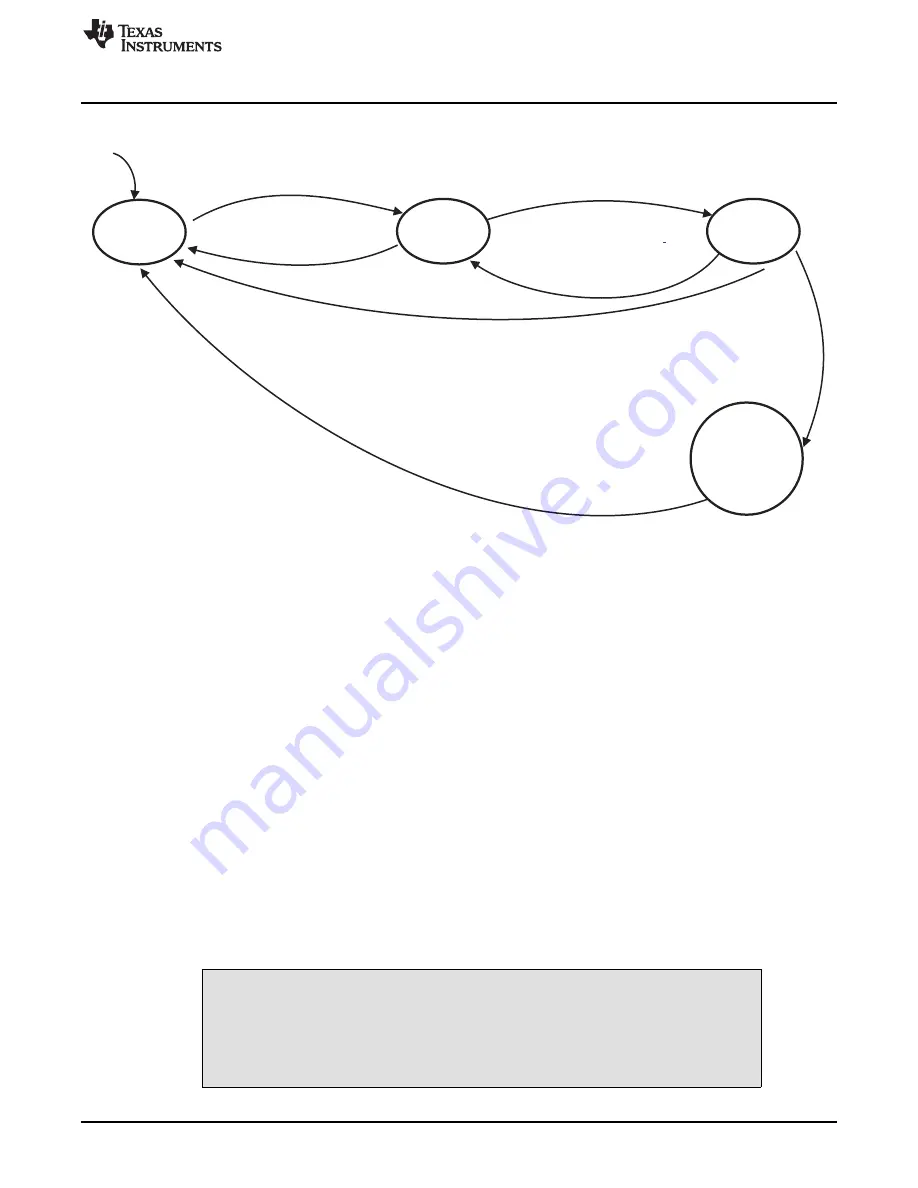

Timer started

Timer loaded

DSI_TIMING[15] LP_RX_TO = 0x0

by software

DSI_TIMING2[15] LP_RX_TO = 0x1

RESET

DSI_TIMING2[15] LP_RX_TO = 0x0 by software

LP RX timer has completed.

Time-out

IDLE

DSI_TIMING2[15] LP_RX_TO = 0x0 by hardware

Direction has changed (RX >TX).

LP_RX_TO

interrupt

generation and

ForceTxStopMode

sequence

dss-175

Public Version

www.ti.com

Display Subsystem Functional Description

Figure 7-99. Low-Power RX Timer FSM

When the interrupt is generated, the hardware should automatically reset the DSS.

LP_RX_TO bit and then assert ForceTXStopMode in order for the DSI complex I/O to drive LP-11 stop

state. The ForceTXStopMode timer is used to define the minimum duration of LP-11 state. The Stop State

can be longer if there is no activity.

The hardware resets the ForceTXStopMode bit, followed by an internal logic reset except all register

values and TX FIFO content, then resets the DSS.

[0] IF_EN bit. The software should take

action to recover by resetting the peripheral, for example, if it is not responding. It should wait for the

DSS.

[15] FORCE_TX_STOP_MODE_IO and DSS.

[0] IF_EN bits to be reset

before starting the recovery sequence. The TX FIFO is not flushed (the FIFO is flushed only when

DSS.

[0] VC_EN is set to 1).

7.4.3.8

Bus Turnaround

The bus turn-around (BTA) is not automatically sent by default after each packet sent to the display(s). It

is programmable independently for each VC ID. The VC can be enabled when DSS.

[6]

BTA_EN bit is set to 1 by software. The software should ensure that, when the BTA is sent to the

peripheral, there is enough time allocated for the response and the BTA from the peripheral to host. For

more information about possible DSI PHY timing adjustments during the turn-around procedure, see

, Turn-Around Request in Transmit Mode, and

,Turn-Around Request in

Receive Mode. When setting the DSS.

[6] BTA_EN bit to 1, one BTA is sent manually to

the peripheral. This manual mode can be used for packets in command or video mode.

Acknowledgment from the peripheral for successful BTA is indicated by asserting the BTA_IRQ interrupt, if

it is enabled in the DSS.

[5] BTA_IRQ_EN bit. To monitor the BTA interrupt, the

user should read the DSS.

[5] BTA_IRQ status bit.

CAUTION

The BTA should not be sent when the RX FIFO is not empty. Users should take

care of emptying the RX FIFO before sending BTA to the peripheral. It is to

ensure that when receiving new data from peripheral, all the allocated spaces

for all the VCs are empty.

1679

SWPU177N – December 2009 – Revised November 2010

Display Subsystem

Copyright © 2009–2010, Texas Instruments Incorporated

Содержание OMAP36 Series

Страница 174: ...174 List of Tables SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 692: ...692 MPU Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1084: ...1084 IVA2 2 Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1990: ...1990 2D 3D Graphics Accelerator SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2334: ...2334 Memory Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2700: ...2700 Memory Management Units SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2868: ...2868 HDQ 1 Wire SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2974: ...2974 UART IrDA CIR SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3054: ...3054 Multichannel SPI SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3462: ...3462 MMC SD SDIO Card Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3508: ...3508 General Purpose Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3584: ...3584 Initialization SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3648: ...3648 Debug and Emulation SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...