Maintenance-Object Repair Procedures

555-233-143

8-1530

Issue 1 May 2002

■

Replace the active Expansion Interface circuit pack in the

master port network.

■

In a CSS configuration, replace the Switch Node Interface

circuit pack connected to the active Expansion Interface

circuit pack in the master port network. The list fiber-link

command can be used to determine the Switch Node

Interface circuit pack that is connected to the active

Expansion Interface circuit pack in the master port network.

■

If the system’s synchronization reference is a Tone-Clock

circuit pack or a Stratum-3 clock, follow normal escalation

procedures.

If the system’s primary synchronization reference is a DS1

Interface circuit pack, assign a different DS1 Interface as the

primary reference. If the problem persists and any slip errors

remain, follow the procedures described in the

troubleshooting section above.

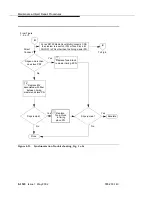

6. For unduplicated Tone-Clock circuit packs in a slave port network:

■

Enter set tone-clock UUC command to switch the

Tone-Clock in the master port network.

■

If the problem still persists, enter set tone-clock UUC to

switch the Tone-Clocks in the master port network back to

their previous configuration.

Enter the test Tone-Clock UUC long command to test the

Tone-Clock in the master and slave port networks.

Check the Error Log for TDM-CLK errors and verify that TDM

Bus Clock Circuit Status Inquiry test (#148) passes.

If Test #148 fails with an Error Code 2–32, see

to resolve the problem. If not, continue

with the following steps.

■

If the master and slave Tone-Clock circuit packs do not fail

TDM Bus Clock Test #150 (TDM Bus Clock PPM Inquiry

test), replace the Expansion Interface circuit packs that have

EXP-INTF error 2305.

■

If the system synchronization reference is a Tone-Clock

circuit pack and the master Tone-Clock circuit pack fails TDM

Bus Clock Test #150, follow the steps listed in “TDM-CLK” to

replace the master Tone-Clock circuit pack.

■

If the system’s synchronization reference is a DS1 Interface

circuit pack and the master Tone-Clock circuit pack fails TDM

Bus Clock test (#150), the primary or secondary (if

administered) synchronization references are not providing

valid timing signals for the system.

Содержание S8700 Series

Страница 50: ...Maintenance Architecture 555 233 143 1 26 Issue 1 May 2002 ...

Страница 74: ...Initialization and Recovery 555 233 143 3 12 Issue 1 May 2002 ...

Страница 186: ...Alarms Errors and Troubleshooting 555 233 143 4 112 Issue 1 May 2002 ...

Страница 232: ...Additional Maintenance Procedures 555 233 143 5 46 Issue 1 May 2002 ...

Страница 635: ...status psa Issue 1 May 2002 7 379 555 233 143 status psa See status tti on page 7 406 ...

Страница 722: ...Maintenance Commands 555 233 143 7 466 Issue 1 May 2002 ...

Страница 1121: ...CARR POW Carrier Power Supply Issue 1 May 2002 8 399 555 233 143 Figure 8 19 Power Distribution Unit J58890CH 1 ...

Страница 1447: ...E DIG RES TN800 reserve slot Issue 1 May 2002 8 725 555 233 143 E DIG RES TN800 reserve slot See ASAI RES ...

Страница 1735: ...LGATE AJ Issue 1 May 2002 8 1013 555 233 143 LGATE AJ See BRI SET LGATE BD See BRI BD LGATE PT See BRI PT ...

Страница 1846: ...Maintenance Object Repair Procedures 555 233 143 8 1124 Issue 1 May 2002 Figure 8 62 TN787 MMI MULTIMEDIA INTERFACE CIRCUIT PACK ...