Rev. 1.0, 02/00, page 324 of 1141

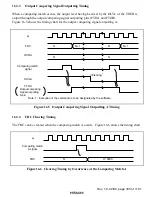

16.2.5

Timer Control/Status Register X (TCSRX)

0

0

1

0

2

0

3

0

4

0

5

0

6

0

7

R/W

R/(W)*

ICFB

0

R/(W)*

ICFA

R/(W)*

ICFD

R/(W)*

ICFC

R/(W)*

OCFB

R/(W)*

OCFA

CCLRA

R/(W)*

OVF

Note: * Only 0 can be written to clear the flag for Bits 7 to 1.

Bit :

Initial value :

R/W :

The TCSRX is an 8-bit register which works to select counter clearing timing and to control

respective interrupt requesting signals. The TCSRX is initialized to H'00 when reset or under the

standby mode, watch mode, subsleep mode, module stop mode or subactive mode.

Meanwhile, as for the timing, see section 16.3, Operation.

The FTIA through FTID pins are for fixed inputs inside the LSI under the low power consumption

mode excluding the sleep mode. Consequently, when such shifts as active mode

→

low power

consumption mode

→

active mode are made, wrong edges may be detected depending on the pin

status or on the type of the detecting edge.

To avoid such error, clear the interrupt requesting flag once immediately after shifting to the

active mode from the low power consumption mode.

Bit 7

Input Capture Flag A (ICFA): This is a status flag indicating the fact that the value of

the FRC has been transferred to the ICRA by the input capture signals.

When the BUFEA of the TCRX is being set to 1, the ICFA indicates the status that the FRC value

has been transferred to the ICRA by the input capture signals and that the ICRA value before

being updated has been transferred to the ICRC.

This flag should be cleared by use of of the software. Such setting should only be made by use of

the hardware. It is not possible to make this setting using a software.

Bit 7

ICFA

Description

0

[Clearing conditions]

(Initial value)

When 0 is written into the ICFA after reading the ICFA under the setting of ICFA = 1

1

[Setting conditions]

When the value of the FRC has been transferred to the ICRA by the input capture

signals