Rev. 1.0, 02/00, page 1038 of 1141

H'D101: Timer Control/Status Register X TCSRX: Timer X1

0

0

1

0

2

0

3

0

4

0

5

0

6

0

7

R/ W

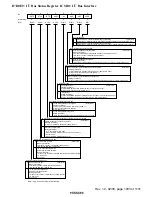

R/(W)*

ICFB

0

R/(W)*

ICFA

R/(W)*

ICFD

R/(W)*

ICFC

R/(W)*

OCFB

R/(W)*

OCFA

CCLRA

R/(W)*

OVF

Note: * Only 0 can be written to bits 7 to 1 to clear the flags.

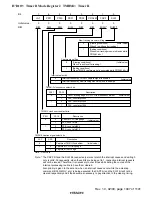

Output compare flag A

[Clearing conditions]

When 0 is written to OCFA after reading

OCFA = 1

(Initial value)

[Setting conditions]

When FRC = OCRA

0

1

Output compare flag B

[Clearing conditions]

When 0 is written to OCFB after reading

OCFB = 1

(Initial value)

[Setting conditions]

When FRC = OCRB

0

1

Timer overflow

[Clearing conditions]

When 0 is written to OVF after reading

OVF = 1

(Initial value)

[Setting conditions]

When FRC changes from H'FFFF to

H'0000

0

1

Input capture flag D

[Clearing conditions]

When 0 is written to ICFD after reading

ICFD = 1

(Initial value)

[Setting conditions]

When input capture signal is generated

0

1

Input capture flag C

[Clearing conditions]

When 0 is written to ICFC after reading

ICFC = 1

(Initial value)

[Setting conditions]

When input capture signal is generated

0

1

Input capture flag B

[Clearing conditions]

When 0 is written to ICFB after reading

ICFB = 1

(Initial value)

[Setting conditions]

When FRC value is transferred to ICRB by

input capture signal

0

1

Input capture flag A

[Clearing conditions]

When 0 is written to ICFA after reading

ICFA = 1

(Initial value)

[Setting conditions]

When FRC value is transferred to ICRA by

input capture signal

0

1

Counter clear

FRC clearing is disabled

(Initial value)

FRC clearing is enabled

0

1

Initial value :

Bit

R/W

:

: