Rev. 1.0, 02/00, page 667 of 1141

Offset (DOfp, DOfs, COfp, COfs)

*

W

13

*

W

14

*

W

15

1

0

3

2

5

4

7

*

W

6

*

W

9

*

W

8

*

W

11

*

W

10

*

W

*

W

W

W

W

W

W

W

12

*

*

*

*

*

*

Bit :

Initial value :

R/W :

Note: * Initial value is uncertain.

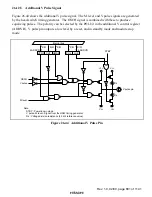

These registers are 16-bit write-only buffers that set offset level of digital filter output. Only a

word access is valid. If a byte access is attempted, correct operation is not guaranteed. If a read is

attempted, an undetermined value is read out.

These registers are not initialized by a reset or in standby mode. Be sure to write data in them

before processing starts.

In this digital filter, output gain adjustment (

×

1, 2, 4, 8 ,16, 32, 64) after offset adding is enabled.

Take output gain into account when setting accumulation gain.

Delay Initialization Register (CZp, CZs, DZp, DZs)

13

14

15

1

0

3

2

5

4

7

0

W

6

0

W

9

0

W

8

0

W

11

0

W

10

0

W

W

W

W

W

W

W

12

0

0

0

0

0

0

1

1

1

1

—

—

—

—

Bit :

Initial value :

R/W :

The delay initialization register is a 16-bit write-only register. Only a word access is valid. If a

byte access is attempted, correct operation is not guaranteed. If a read is attempted, an

undetermined value is read out.

It is initialized to H'F000 by a reset, or in stand-by or module stop mode. The MSB of 12-bit data

(bit 11) is a sign bit.

Loading to Z

-1

is performed automatically by bits 4 and 3 of CFIC and DFIC (CZPON, CZSON,

DZPON, DZSON). Writing in register is always available, but loading in Z

-1

is not possible when

the digital filter is performing computation in relation to such register. In such a case, loading to

Z

-1

will be done the next time computation begins.