Rev. 1.0, 02/00, page 715 of 1141

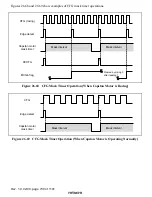

The 16-bit counter in the REC-CTL circuit continues counting on a clock derived by dividing the

system clock

φ

s (= f

OSC

/2) by 4. The counter is cleared on the rise of REF30X in record mode, and

on the rise of PB-CTL in rewrite mode. REC-CTL match detection is carried out by comparing

the counter value with each RCDR value.

RCDR1 to RCDR5 can be written to by software at all times. If RCDR is changed before the

respective match detection is performed, match detection is performed using the new value. The

value changed after match detection becomes valid on the rise of REF30X following the change.

Figure 26.61 shows examples of RCDR change timing.

REF30X

REC-CTL

RCDR1 RCDR2

RCDR1

1 pulse (Short)

0 pulse (Short)

Rewritten 0 pulse

(Short)

RCDR1

RCDR1

Counter

RCDR4

RCDR2

RCDR1

RCDR4

RCDR4

RCDR4

Interval in which

RCDR4 can be

written to

Figure 26.61 Example of RCDR Change Timing (Example Showing RCDR4)