Rev. 1.0, 02/00, page 318 of 1141

16.2.2

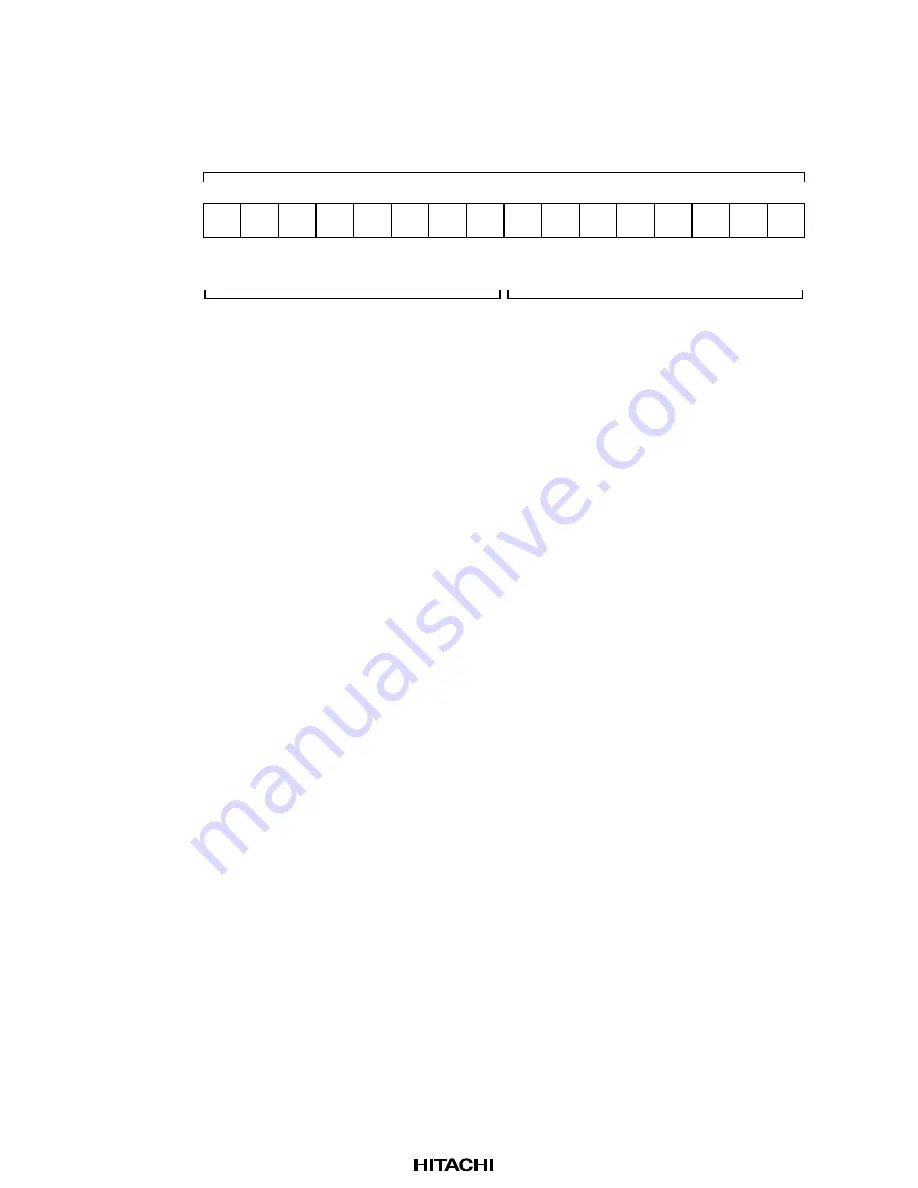

Output Comparing Registers A and B (OCRA and OCRB)

Output comparing register AH and BH (OCRAH and OCRBH)

Output comparing register AL and BL (OCRAL and OCRBL)

1

3

1

R/W

5

1

R/W

7

1

9

1

R/W

11

1

13

1

15

R/W

R/W

R/W

1

R/W

R/W

1

1

2

1

R/W

4

1

R/W

6

1

8

1

R/W

10

1

12

1

14

OCRA, OCRB

OCRAH, OCRBH

OCRAL, OCRBL

R/W

R/W

R/W

R/W

1

R/W

0

Bit :

Initial value :

R/W :

The OCR consists of twin 16-bit read/write registers (OCRA and OCRB). The contents of the

OCR are always being compared with the FRC and, when the value of these two match, the OCFA

and OCRB of the TCSRX will be set to 1. At this time, if the OCIAE and OCIB of the TIER are

being set to 1, an interrupt request will be issued to the CPU.

When performing compare matching, if the OEA and OEB of the TOCR are set to 1, the level

value set to the OLVLA and OLVLB of the TOCR will be output through the FTOA and FTOB

pins. After resetting, 0 will be output through the FTOA and FTOB pins until the first compare

matching occurs.

Reading/writing can be made from and to the OCR through the CPU at 8-bit or 16-bit.

The OCR is cleared to H'FFFF when reset or under the standby mode, watch mode, subsleep

mode, module stop mode or subactive mode.