Rev. 1.0, 02/00, page 1 of 1141

Section 1 Overview

1.1

Overview

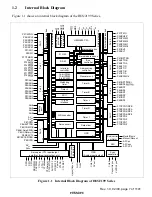

The H8S/2199 Series comprise microcomputers (MCUs) built around the H8S/2000 CPU,

employing Hitachi's proprietary architecture, and equipped with supporting modules on-chip.

The H8S/2000 has an internal 32-bit architecture, is provided with sixteen 16-bit general registers

and a concise, optimized instruction set designed for high-speed operation, and can address a 16-

Mbyte linear address space. The instruction set is upward-compatible with H8/300 and H8/300H

CPU instructions at the object-code level, facilitating migration from the H8/300, H8/300L, or

H8/300H Series.

The H8S/2199 Series is equipped with a digital servo circuit, sync separator, OSD, data slicer,

ROM, RAM, seven types of timers, three types of PWM, two types of serial communication

interface, an I

2

C bus interface, A/D converter, and I/O port as on-chip supporting modules.

The on-chip ROM is either flash memory (F-ZTAT

*) or mask ROM, with a capacity of 128,

112, 96, or 80 kbytes. ROM is connected to the CPU via a 16-bit data bus, enabling both byte and

word data to be accessed in one state. Instruction fetching has been speeded up, and processing

speed increased.

The features of the H8S/2199 Series are shown in table 1.1.

Note: * F-ZTAT

is a trademark of Hitachi, Ltd.