Rev. 1.0, 02/00, page 639 of 1141

26.8.2

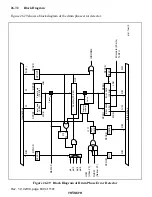

Block Diagram

Figure 26.32 shows a block diagram of the capstan speed error detector.

W

W

R

UDF

OVF

Lock 2 up

Clear

Latch

Preset

CFVCR

CFRLDR

CFVCR

CFPR

CFVCR

CFVCR

CFVCR

CFUCR

CFER

CFRVCR

Error data

(16 bits)

To DFU

DVCFG

CFRUDR

Internal bus

R/W

Internal bus

R/W

W

R/W

R/W

R/W

R/W

(R)/W

Lock 1 up

S

R

F/F

Q

S

R

F/F

CFRCS1,0

CF-R/UNR

Lock counter

(2 bits)

Q

S

R

F/F

Q

Lock range

detector

Lock range data (16 bits)

Lock range data (16 bits)

CPCNT

Error data

limiter

control

circuit

CFRFON

CFESS

Error data (16 bits)

Counter (16 bits)

CFOVF

IRRCAP2

IRRCAP1

CROCKON

To DFU

Preset data (16 bits)

CFCS1,0

φ

s

φ

s/2

φ

s/4

φ

s/8

Figure 26.32 Block Diagram of Capstan Speed Error Detector