Rev. 1.0, 02/00, page 948 of 1141

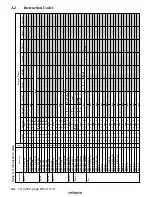

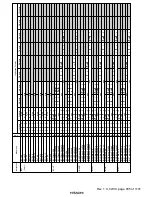

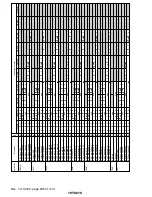

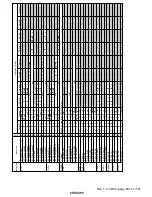

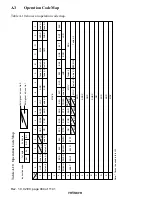

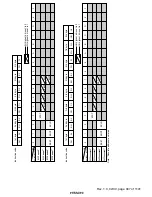

A.4

Number of Execution States

This section explains execution state and how to calculate the number of execution states for each

instruction of the H8S/2000 CPU.

Table A.12 indicates number of cycles of instruction fetch and data read/write during instruction

execution, and table A.11 indicates number of states required for each instruction size.

The number of execution states can be obtained from the equation below.

Number of execution states = I

⋅

S

I

+ J

⋅

S

J

+ K

⋅

S

K

+ L

⋅

S

L

+ M

⋅

S

M

+ N

⋅

S

N

Examples of Execution State Number Calculation

The conditions are as follows: In advanced mode, program and stack areas are set in the on-chip

memory, a wait is inserted every 2 states in the on-chip supporting module access with 8-bit bus

width.

1. BSET #0, @FFFFC7:8

From Table A.12,

I = L = 2, J = K = M = N = 0

From Table A.11,

S

I

= 1, S

L

= 2

Number of execution states = 2

×

1 + 2

×

2 = 6

2. JSR @@30

From Table A.12,

I = J = K = 2, L = M = N = 0

From Table A.11,

S

I

= S

J

= S

K

= 1

Number of execution states = 2

×

1 + 2

×

1 + 2

×

1 = 6