Rev. 1.0, 02/00, page 1055 of 1141

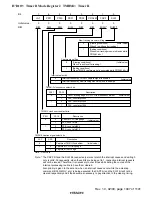

H'D135: A/D Control/Status Register ADCSR: A/D Converter

0

0

1

0

R

2

0

R

3

0

4

0

R/W

5

0

6

7

R/(W)*

R

R/W

ADIE

0

R/(W)*

SEND

SST

HST

BUSY

SCNL

HEND

1

A/D interrupt enable bit

0 Interrupt (ADI) upon A/D conversion end is disabled

(Initial value)

1 Interrupt (ADI) upon A/D conversion end is enabled

Software A/D start flag

0 Read: Indicates that software-triggered A/D conversion

has ended or been stopped

(Initial value)

Write: Software-triggered A/D conversion is aborted

1 Read: Indicates that software-triggered A/D conversion

is in progress

Write: Starts software-triggered A/D conversion

Busy flag

0 No contention for A/D conversion

(Initial value)

1 Indicates an attempt to execute software-triggered

A/D conversion while hardware- or external-triggered

A/D conversion was in progress.

Software-triggered A/D conversion cancel flag

0 No contention for A/D conversion

(Initial value)

1 Indicates that software-triggered A/D

conversion was canceled by the start of

hardware-triggered A/D conversion.

Hardware A/D status flag

0 Read: Hardware- or external -triggered A/D conversion is

not in progress

(Initial value)

Write: Hardware- or external-triggered A/D conversion is

aborted

1 Hardware- or external-triggered A/D conversion is in

progress.

Software A/D end flag

0 [Clearing conditions]

(Initial value)

When 0 is written after reading 1

1 [Setting conditions]

When software-triggered A/D conversion has ended

Hardware A/D end flag

0 [Clearing conditions]

(Initial value)

When 0 is written after reading 1

1 [Setting conditions]

When hardware- or external-triggered A/D

conversion has ended

Initial value :

—

—

Note: * Only 0 can be written to clear the flag.

Bit

R/W

:

: