Rev. 1.0, 02/00, page 641 of 1141

26.8.4

Register Description

Specified CFG Speed Preset Data Register (CFPR)

8

0

9

0

W

10

0

W

11

0

12

0

W

0

W

13

14

0

15

CFPR12

CFPR11

CFPR10

CFPR9

CFPR8

0

W

CFPR15

W

W

W

CFPR14

CFPR13

Bit :

Initial value :

R/W :

0

0

1

0

W

2

0

W

3

0

4

0

W

0

W

5

6

0

7

CFPR4

CFPR3

CFPR2

CFPR1

CFPR0

0

W

CFPR7

W

W

W

CFPR6

CFPR5

Bit :

Initial value :

R/W :

The 16-bit preset data that defines the specified CFG speed is set in CFPR. When data is written,

the 16-bit preset data is sent to the preset circuit. The preset data can be calculated from the

following equation by using H'8000* as the reference value.

φ

s/n

CFG speed preset data

= H '

8000

−

(

−

2)

DVCFG frequency

φ

s:

Servo clock frequency in Hz (f

OSC

/2)

DVCFG frequency: In Hz

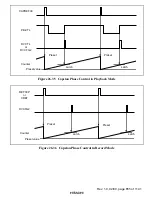

The constant 2 is the preset interval (see figure 26.33).

φ

s/n:

Clock source of the selected counter

CFPR is a 16-bit write-only register. Only a word acces is valid. If a byte access is attempted,

correct operation is not guaranteed. CFPR is initialized to H'0000 by a reset.

Note: The preset data value is calculated so that the counter will reach H'8000 when the error is

zero. When the counter value is latched as error data in the CFG speed error data register

(CFER), however, it is converted to a value referenced to H'0000.