Rev. 1.0, 02/00, page 7 of 1141

1.2

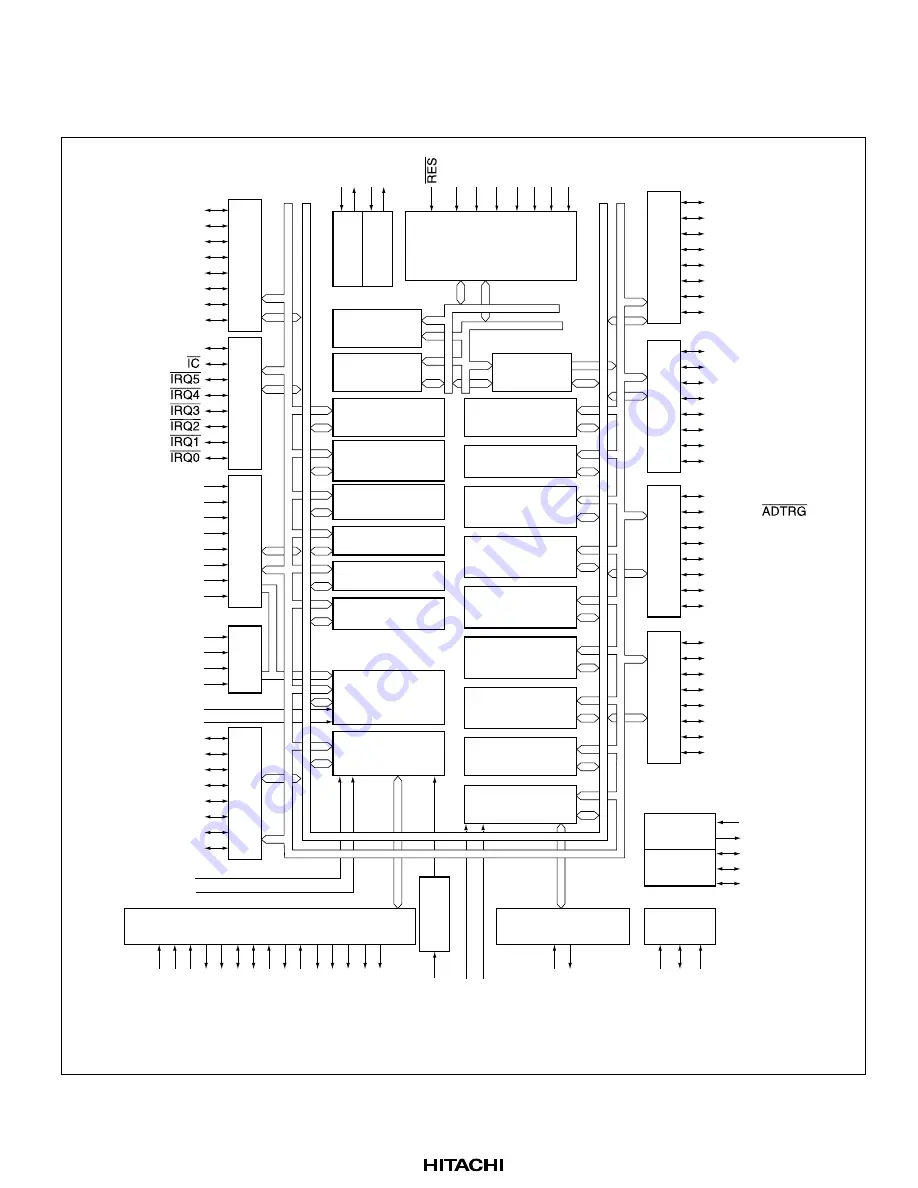

Internal Block Diagram

Figure 1.1 shows an internal block diagram of the H8S/2199 Series.

P23/SDA1

P25/SDA0

P22/SCK1

P26/SCL0

P21/SO1

P27/SYNCI

P20/SI1

P24/SCL1

V

SS

VCL

V

SS

V

CC

V

SS

V

CC

MD0

OSC2

OSC1

X2

X1

Hsync(Csync)

Sync signal

detection

OV

CC

OV

SS

SV

SS

SV

CC

CAPPWM

CTL(+)

CTLSMT(i)

CTLBias

CVin2

Csync/Hsync

VLPF/Vsync

CTL(–)

AUDIO FF

VIDEO FF

Vpulse

CTL FB

CTL REF

CTLAmp(o)

DFG

CFG

DRMPWM

DPG

P13/

P15/

P12/

Interrupt

controller

R A M

R O M

Internal data bus

External data bus

External address bus

External data bus

External address bus

Internal address bus

Servo pins (CTL input/output

amplifier, three-level output, etc.)

CVin1

CVout

OSD

(Analog input/output)

Sync

separation

Sub-carrier

oscillator

AFC

H8S/2000 CPU

Bus

controller

Address trap

controller

P16/

P11/

P17/TMOW

P10/

P14/

P03/AN3

P05/AN5

P02/AN2

P06/AN6

P01/AN1

P07/AN7

P00/AN0

P04/AN4

ANA

AN9

AN8

ANB

AV

CC

AV

SS

P83/C.Rotary/R

P85/COMP/B

P82/EXCTL

P86/EXTTRG

P81/EXCAP/YBO

P87/DPG

P80/YCO

P84/H.Amp SW/G

P33/PWM1

P35/PWM3

P32/PWM0

P36/BUZZ

P31/SV2

P37/TMO

P30/SV1

P34/PWM2

P43/FTIC

P45/FTOA

P42/FTIB

P46/FTOB

P41/FTIA

P47/RPTRG

P40/PWM14

P44/FTID

P73/PPG3

P75/PPG5/RP9

P72/PPG2

P76/PPG6/RPA

P71/PPG1

P77/PPG7/RPB

P70/PPG0

P74/PPG4/RP8

4fscout/2fscout

AFC pc

AFC osc

AFC LPF

4fscin/2fscin

P63/RP3

P65/RP5

P62/RP2

P66/RP6/

P61/RP1

P67/RP7/TMBI

P60/RP0

P64/RP4

14-bit PWM

12-bit PWM

8-bit PWM

Prescaler unit

Watchdog

timer

Timer L

Timer A

SCI1

Timer B

Timer J

I

2

C bus

interface

Timer R

A/D converter

Timer 1

Port 7

Port 6

Port 4

Port 3

Port 2

Port 1

Port 0

Port 8

Analog

port

Subclock pulse

generator

Subclock pulse pulse generator

Servo circuit

Data slicer

OSD

Figure 1.1 Internal Block Diagram of H8S/2199 Series