Rev. 1.0, 02/00, page 1010 of 1141

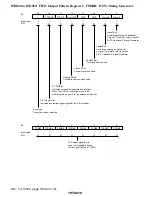

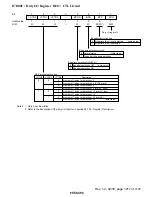

H'D06F: Additional V Control Register ADDVR: Additional V Signal Generator

0

0

1

0

R/W

2

0

R/W

3

0

4

0

R/W

5

1

6

7

R/W

R/W

HMSK

HiZ

CUT

VPOM

POL

1

1

Note: * Don't care.

OSCH mask bit

0 OSCH added

(Initial value)

1 OSCH not added

High impedance bit

0 3-level output from Vpulse pin

(Initial value)

1 Vpulse pin is set as 3-state (H/L/HiZ) pin

Additional V output control bits

CUT VPON POL Description

0 0 * Low level

(Initial value)

1 0 Negative polarity

1 Positive polarity

1 * 0 Immediate level

(high-impedance when HiZ bit = 1)

1 High level

—

—

—

—

—

—

Bit

Initial value

R/W

:

:

:

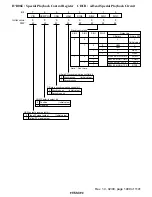

H'D070 to H'D071: X-Value Data Register

XDR: X-Value, TRK-Value Adjustment Circuit

1

13

1

14

1

15

1

0

3

2

5

4

7

0

W

6

0

W

9

0

W

8

0

W

11

0

W

10

0

W

1

W

W

W

W

W

W

12

XD1

XD0

XD3

XD2

XD5

XD4

XD7

XD6

XD9

XD8

XD11 XD10

0

0

0

0

0

0

Bit

Initial value

R/W

:

:

:

—

—

—

—

—

—

—

—

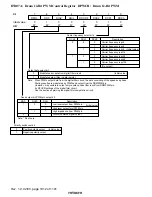

H'D072 to H'D073: TRK-Value Data Register

TRDR: X-Value, TRK-Value Adjustment Circuit

1

13

1

14

1

15

1

0

3

2

5

4

7

0

W

6

0

W

9

0

W

8

0

W

11

0

W

10

0

W

1

W

W

W

W

W

W

12

TRD1 TRD0

TRD3 TRD2

TRD5 TRD4

TRD7 TRD6

TRD9 TRD8

TRD11 TRD10

0

0

0

0

0

0

:

:

:

Bit

Initial value

R/W

—

—

—

—

—

—

—

—