Rev. 1.0, 02/00, page 737 of 1141

Horizontal Sync Signal Threshold Register (HTR)

0

0

1

0

W

2

0

W

3

0

4

5

6

1

7

—

—

—

—

—

—

—

—

W

W

HTR3

HTR2

HTR1

HTR0

1

1

1

Bit :

Initial value :

R/W :

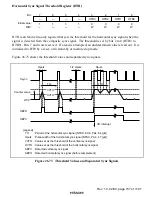

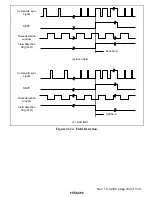

HTR is an 8-bit write-only register that sets the threshold for the horizontal sync signal when the

signal is detected from the composite sync signal. The threshold is set by bits 3 to 0 (HTR3 to

HTR0). Bits 7 and 4 are reserved. If a read is attempted, an undetermined value is read out. It is

initialized to H'F0 by a reset, or in stand-by or module stop mode.

Figure 26.73 shows the threshold values and separated sync signals.

[Legend]

TH

Hpuls

T H

SEPV

Hpuls

: Period of the horizontal sync signal (NTSC: 63.6, PAL: 64 [

µ

s])

: Pulse width of the horizontal sync signal (NTSC, PAL: 4.7 [

µ

s])

VVTH

HVTH

: Value set as the threshold of the vertical sync signal

: Value set as the threshold of the horizontal sync signal

SEPV

SEPH

: Detected vertical sync signal

: Detected horizontal sync signal (before complement)

T H

SEPH

Csync

H'00

Counter value

1/2 Hpuls

VD interrupt

Hpuls

VVTH

HVTH

Figure 26.73 Threshold Values and Separated Sync Signals