Rev. 1.0, 02/00, page 55 of 1141

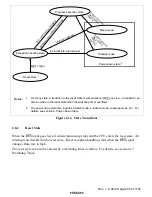

Reset state

Exception-handling state

Sleep mode

Standby mode

Power-down state

Program execution state

Interrupt request

External interrupt request

= High

Request for exception handling

SLEEP instruction

with LSON=0,

SSBY=1,

TMA3=0

SLEEP instruction

with LSON=0,

SSBY=0

Notes:

End of exception handling

*1

*2

1.

2.

From any state, a transition to the reset state occurs whenever

goes low. A transition can

also be made to the reset state when the watchdog timer overflows.

The power-down state also includes a watch mode, subactive mode, subsleep mode, etc. For

details, see section 4, Power-Down State.

Figure 2.16 State Transitions

2.8.2

Reset State

When the

5(6

input goes low all current processing stops and the CPU enters the reset state. All

interrupts are disabled in the reset state. Reset exception handling starts when the

5(6

signal

changes from low to high.

The reset state can also be entered by a watchdog timer overflow. For details, see section 17,

Watchdog Timer.