Rev. 1.0, 02/00, page 181 of 1141

9.4

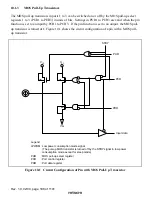

Duty Adjustment Circuit

When the oscillator frequency is 5 MHz or higher, the duty adjustment circuit adjusts the duty

cycle of the clock signal from the oscillator to generate the system clock (

φ

).

9.5

Medium-Speed Clock Divider

The medium-speed divider divides the system clock to generate

φ

/16,

φ

/32, and

φ

/64 clocks.

9.6

Bus Master Clock Selection Circuit

The bus master clock selection circuit selects the system clock (

φ

) or one of the medium-speed

clocks (

φ

/16,

φ

/32 or

φ

/64) to be supplied to the bus master (CPU), according to the settings of bits

SCK2 to SCK0 in SBYCR.