Rev. 1.0, 02/00, page 337 of 1141

Even when the ICRC or ICRD is used as the buffer register, the input capture flag will be set up

corresponding to the designated edge change of respective input capture signals.

For example, when using the ICRC as the buffer register for the ICRA, when an edge change

having been designated by the IEDGC bit is detected with the input capture signals C and if the

ICIEC bit is duly set, an interrupt request will be issued.

However, in this case, the FRC value will not be transferred to the ICRC.

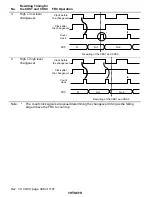

16.3.6

Input Capture Flag (ICFA through ICFD) Setting Up Timing

The input capture signal works to set the ICFA through ICFD to 1 and, simultaneously, the FRC

value is transferred to the corresponding ICRA through ICRD. Figure 16.9 shows the timing

chart.

Input capture

signal

ICFA to ICFD

ICRA to ICRD

FRC

N

N

φ

Figure 16.9 ICFA through ICFD Setting Up Timing