Rev. 1.0, 02/00, page 535 of 1141

25.3

Precautions in Usage

Address trap interrupt arises 2 states after prefetching the trap address. Trap interrupt may occur

after the trap instruction has been executed, depending on a combination of instructions

immediately preceding the setting up of the address trap.

If the instruction to trap immediately follows the branch instruction or the conditional branch

instruction, operation may differ, depending on whether the condition was satisfied or not, or the

address to be stacked may be located at the branch. Figures 25.2 to 25.22 show specific

operations.

For information as to where the next instruction prefetch occurs during the execution cycle of the

instruction, see appendix A.5 of this manual or section 2.7 Bus State during Execution of

Instruction of the H8S/2600 and H8S/2000 Series Programming Manual. (R:W NEXT is the next

instruction prefetch.)

25.3.1

Basic Operations

After terminating the execution of the instruction being executed in the second state from the trap

address prefetch, the address trap interrupt exception handling is started.

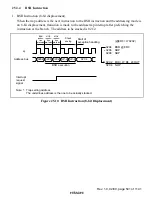

1. Figure 25.2 shows the operation when the instruction immediately preceding the trap address

is that of 3 states or more of the execution cycle and the next instruction prefetch occurs in the

state before the last 2 states. The address to be stacked is 0260.

φ

Address bus

Interrupt

request

signal

MOV

execution

MOV

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

Internal

opera-

tion

Data

read

Start of exception

handling

Immediately

preceding

Instruction

Address

025E MOV.B @ER3+,R2L

0260 NOP

(ER3 = H'0000)

0262 NOP

0264 NOP

025E

0260

0000

0262

*

→

* Trap setting address

The underlines address is the

one to be actually stacked.

Note:

In the figure above, the NOP instruction is used as the typical example of instruction with

execution cycle of 1 state. Other instructions with the execution cycle of 1 state also apply

(Ex. MOV.B, Rs, Rd).

Figure 25.2 Basic Operations (1)