Rev. 1.0, 02/00, page 746 of 1141

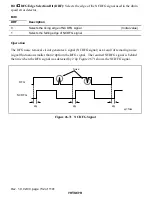

Noise Detection Operation: The noise detector considers an irregular pulse of the composite sync

signal (Csync) and a chip of a horizontal sync signal pulse within a frame as noise. The noise

counter takes counts of the irregular pulses during the high period of the noise detection window

and the chips and drop-outs of the horizontal sync signal pulses during the low period. The noise

detector counts more than one irregular pulses as one. The noise counter is cleared at every frame

(Vsync is detected twice).

The equalizing pulse contained in 9H of the vertical sync signal is counted also as an irregular

pulse.

The noise detection flag (NOIS) in the sync signal control register (SYNCR) is set to 1 if the count

of the irregular the count of the pulse chips and drop-outs of the horizontal sync signal >

4

×

(value of NDR7 to 0).

See the description on the sync signal control register (SYNCR) is section 26.15.5, Register

Description, for the NOIS bit.

Figure 26.76 shows the operation of the noise detection.

Csync

Noise detection

window

Noise detection

flag (NOIS)

Noise counter

Noise detection

level

Noise detection

flag is set.

NOIS : Bit 3 of the sync signal control register (SYNCR)

Noise

Figure 26.76 Operation of the Noise Detection