Rev. 1.0, 02/00, page 1044 of 1141

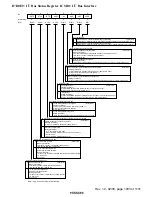

H'D111: Timer Load RegisterB TLB: TimerB

0

0

1

0

W

2

0

W

3

4

5

0

6

0

7

W

W

TLB15

0

W

TLB14

0

W

TLB13

W

TLB16

0

W

TLB17

TLB12

TLB11

TLB10

Bit :

Initial value :

R/W :

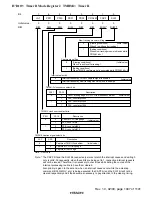

H'D112: Timer L Mode Register LMR: Timer L

0

0

1

0

R/W

2

0

R/W

3

0

4

1

5

1

6

0

7

R/W

R/W

R/W

LMIE

0

R/(W)*

LMIF

LMR3

LMR2

LMR1

LMR0

Note: * Only 0 can be written to clear the flag.

Timer L interrupt request flag

[Clearing conditions]

(Initial value)

When 0 is written after reading 1

[Setting conditions]

When LTC overflow, underflow or compare

match clear occurs

0

1

Timer L interrupt enable bit

Timer L interrupt request is disabled

(Initial value)

Timer L interrupt request is enabled

0

1

Up count control

(Initial value)

Down count control

0

1

Up/down count control

Clock select bit

Clock select

0

0

0

Count at rising edge of PB and REC-CTL

(Initial value)

LMR1

LMR0

LMR2

1

Count at falling edge of PB and REC-CTL

1

*

Count DVCFG2

0

1

*

Internal clock: Count at

φ

/128

1

*

Internal clock: Count at

φ

/64

Note: * Don't care.

—

—

—

—

Bit

Initial value

R/W

:

:

: