Rev. 1.0, 02/00, page 716 of 1141

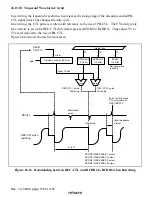

26.13.10 Trapezoid Waveform Circuit

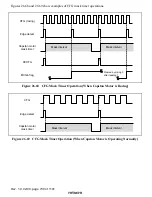

In rewriting, the trapezoid waveform circuit leaves the rising edge of the already-recorded PB-

CTL signal intact, but changes the duty cycle.

In rewriting, the CTL pulse is written with reference to the rise of PB-CTL. The CTL duty cycle

for a rewrite is set in the REC-CTL duty data registers (RCDR2 to RCDR5). Time values T2 to

T5 are referenced to the rise of PB-CTL.

Figure 26.62 shows the rewrite waveform.

W

Internal bus

RCDR3or5

(12 bits)

W

Not used when

rewriting

RCDR2or4

(12 bits)

Up/Down counter (16 bits)

Clear

Upper 12 bits

REC-CTL 0 pulse

fall timing

REC-CTL 1 pulse

fall timing

RESET

PB-CTL

↑

W

T

2

to T

5

Eliminated

pulse

High-impedance

interval

End of writing of one

CTL pulse (except

VISS) IRRCTL

RCDR1

(12 bits)

φ

s/4

Compare

Compare

RCDR2 (BISS/VASS S1 pulse)

RCDR3 (VISS/VASS L1 pulse)

RCDR4 (VISS/VASS S0 pulse)

RCDR5 (VISS/VASS L0 pulse)

PB-CTL

REC-CTL when

rewriting

New pulse

Figure 26.62 Relationship between REC-CTL and RCDR2 to RCDR5 when Rewriting