Rev. 1.0, 02/00, page 860 of 1141

Bit 0

Master-Slave RAM Transfer State Bit (VACS): Is set to 1 if the CPU accesses

OSDRAM during transfer of data from master RAM to slave RAM; the access is invalid. This bit

is not cleared automatically, and so should be cleared by writing 0.

Bit 0

VACS

Description

0

The CPU did not access OSDRAM during data transfer

(Initial value)

1

The CPU accessed OSDRAM during data transfer; the access is invalid

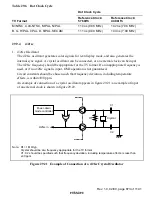

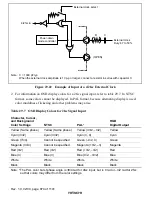

29.7

Digital Output

29.7.1

R, G, and B Outputs

R, G, and B outputs consist of display data in dot units for characters, background, cursors and

other display elements.

Either of two output methods can be selected by the R, G, B digital output specification bit:

characters only, or output of display data for all elements, including characters, borders, cursors,

background, and buttons. Here data for borders and buttons is output as white-equivalent (R=1,

G=1, B=1) or as black-equivalent (R=0, G=0, B=0) data.

The digital output blink control bit is used to select blinking for R, G, and B. The R, G, and B

outputs are multiplexed with port 8 inputs/outputs. For details on pin function selection, refer to

section 10.9, Port 8.

Display data RAM and the screen control register settings are output as display data output for

characters, cursors and background in superimposed mode; this differs from the output data from

the CVout pin.

Examples of R, G, B output are shown in figures 29.12 and 29.13.