Rev. 1.0, 02/00, page xii of 19

22.3.4

Operation in Synchronous Mode ...................................................................... 442

22.4

SCI Interrupts.................................................................................................................... 450

22.5

Usage Notes ...................................................................................................................... 451

Section 23 I

2

C Bus Interface (IIC)

................................................................................. 459

23.1

Overview........................................................................................................................... 459

23.1.1

Features............................................................................................................. 459

23.1.2

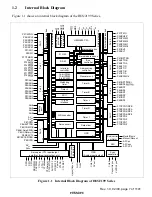

Block Diagram.................................................................................................. 460

23.1.3

Pin Configuration ............................................................................................. 461

23.1.4

Register Configuration...................................................................................... 462

23.2

Register Descriptions ........................................................................................................ 463

23.2.1

I

2

C Bus Data Register (ICDR) .......................................................................... 463

23.2.2

Slave Address Register (SAR).......................................................................... 466

23.2.3

Second Slave Address Register (SARX) .......................................................... 468

23.2.4

I

2

C Bus Mode Register (ICMR)........................................................................ 469

23.2.5

I

2

C Bus Control Register (ICCR)...................................................................... 473

23.2.6

I

2

C Bus Status Register (ICSR)......................................................................... 480

23.2.7

Serial/Timer Control Register (STCR) ............................................................. 484

23.2.8

DDC Switch Register (DDCSWR)................................................................... 485

23.2.9

Module Stop Control Register (MSTPCR)....................................................... 488

23.3

Operation .......................................................................................................................... 489

23.3.1

I

2

C Bus Data Format ......................................................................................... 489

23.3.2

Master Transmit Operation............................................................................... 490

23.3.3

Master Receive Operation ................................................................................ 494

23.3.4

Slave Receive Operation................................................................................... 496

23.3.5

Slave Transmit Operation ................................................................................. 499

23.3.6

IRIC Setting Timing and SCL Control ............................................................. 500

23.3.7

Automatic Switching from Formatless Transfer to I

2

C

Bus Format Transfer ......................................................................................... 502

23.3.8

Noise Canceler.................................................................................................. 503

23.3.9

Sample Flowcharts............................................................................................ 503

23.3.10

Initializing Internal Status................................................................................. 507

23.4

Usage Notes ...................................................................................................................... 509

Section 24 A/D Converter

................................................................................................. 513

24.1

Overview........................................................................................................................... 513

24.1.1

Features............................................................................................................. 513

24.1.2

Block Diagram.................................................................................................. 514

24.1.3

Pin Configuration ............................................................................................. 515

24.1.4

Register Configuration...................................................................................... 516

24.2

Register Descriptions ........................................................................................................ 517

24.2.1

Software-Triggered A/D Result Register (ADR).............................................. 517

24.2.2

Hardware-Triggered A/D Result Register (AHR) ............................................ 517