Rev. 1.0, 02/00, page 793 of 1141

27.3.6

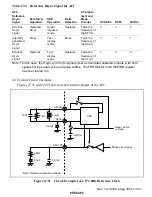

Automatic Frequency Controller (AFC)

The AFC averages the Hsync signal fluctuation of the video signal. Figure 27.20 shows the AFC

configuration. The AFC generates a reference clock having 576 or 448 times the frequency (576

×

fh or 448

×

fh) of the Hsync signal. From this clock, several clocks are generated, such as the

horizontal sync signal (AFCH signal), clock run-in detection window signal, start bit detection

window signal, V complement and mask counter clock when the V complement function is

selected, and the field detection window signal. The reference clock is also used as the dot clock

for the OSD; modifying the reference clock frequency can change the dot width of the character

display. To change the frequency, connect a circuit having a value suitable for the desired

frequency to the AFCosc and AFCpc terminals, and select the division ratio for the frequency-

dividing counter through the setting of the FRQSEL bit in SEPIMR. Note that the data slicer will

not operate when 448

×

fh is selected as the reference clock.

AFCLPF

R

C

VCO

AFCpc

AFCosc

HHK

HSEL

HCKSEL

Masking H

FSC

AFCH

AFC error output circuit

(comparator)

Internal Csync

generator

H complement

and mask

counter

External Hsync

Error signal

Switching

Switching

Reference clock

FRQSEL

Masking and

complementing H

Reference

Hsync signal

Internally generated

Hsync

External Hsync

Signals such

as dot clock

Low pass

filter

Frequency-

dividing counter

(Divided by

576 or 448)

R

Figure 27.20 AFC Configuration