Rev. 1.0, 02/00, page 537 of 1141

25.3.2

Enabling

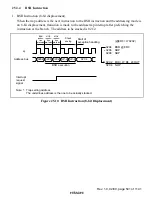

The address trap function becomes valid after executing one instruction following the setting of

the enable bit of the address trap control register (TRCR) to 1.

029C BSET #0, @TRCR

*

029E MOV.W R0, R1

02A0 MOV.B R1L, R3H

02A2 NOP

02A4 CMP.W R0, R1

02A6 NOP

After executing the MOV instruction,

the address trap interrupt does not

arise, and the next instruction is

executed.

Note:

*

Trap setting address

Figure 25.5 Enabling

25.3.3

Bcc Instruction

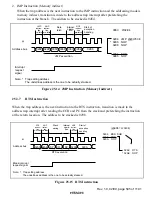

1. When the condition is satisfied by Bcc instruction (8-bit displacement)

If the trap address is the next instruction to the Bcc instruction and the condition is satisfied by

the Bcc instruction and then branched, transition is made to the address trap interrupt after

executing the instruction at the branch. The address to be stacked is 02A8.

φ

Address bus

Interrupt

request

signal

BEQ

execu-

tion

CMP

execu-

tion

029C

02A8

029E 02A6

02AA

029C BEQ NEXT:8

029E NOP

02A0 NOP

02A2 NOP

02A4 NOP

02A6 CMP.W R0, R1

02A8 NOP

(NEXT = H'02A6)

*

Start of

exception

handling

BEQ

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

CMP

instruc-

tion

pre-fetch

Note:

*

Trap setting address

The underlines address is the one to be actually stacked.

Figure 25.6 When the Condition Satisfied by Bcc Instruction (8-bit Displacement)