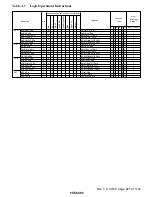

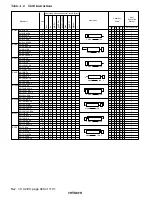

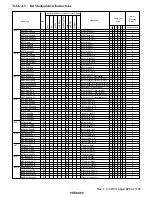

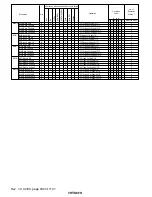

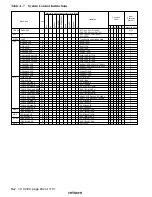

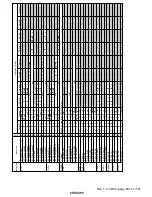

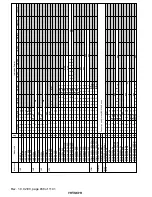

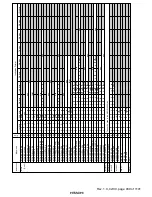

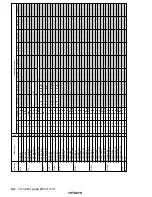

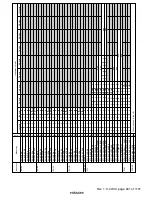

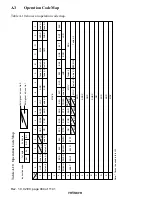

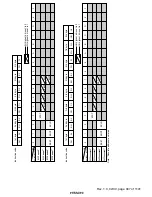

Rev. 1.0, 02/00, page 941 of 1141

SHAL

SHAR

SHLL

SHLR

SLEEP

STC

STM

STMAC

SHAL.B Rd

SHAL.B #2, Rd

SHAL.W Rd

SHAL.W #2, Rd

SHAL.L ERd

SHAL.L #2, ERd

SHAR.B Rd

SHAR.B #2, Rd

SHAR.W Rd

SHAR.W #2, Rd

SHAR.L ERd

SHAR.L #2, ERd

SHLL.B Rd

SHLL.B #2, Rd

SHLL.W Rd

SHLL.W #2, Rd

SHLL.L ERd

SHLL.L #2, ERd

SHLR.B Rd

SHLR.B #2, Rd

SHLR.W Rd

SHLR.W #2, Rd

SHLR.L ERd

SHLR.L #2, ERd

SLEEP

STC.B CCR,Rd

STC.B EXR,Rd

STC.W CCR,@ERd

STC.W EXR,@ERd

STC.W CCR,@(d:16,ERd)

STC.W EXR,@(d:16,ERd)

STC.W CCR,@(d:32,ERd)

STC.W EXR,@(d:32,ERd)

STC.W CCR,@-ERd

STC.W EXR,@-ERd

STC.W CCR,@aa:16

STC.W EXR,@aa:16

STC.W CCR,@aa:32

STC.W EXR,@aa:32

STM.L(ERn-ERn+1) , @-SP

STM.L (ERn-ERn+2) , @-SP

STM.L (ERn-ERn+3) , @-SP

STMAC MACH,ERd

STMAC MACL,ERd

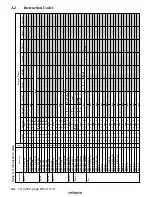

Mnemonic

Instruction Format

1st byte

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

—

B

B

W

W

W

W

W

W

W

W

W

W

W

W

L

L

L

L

L

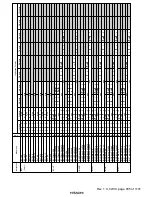

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

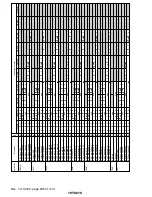

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

8

C

9

D

B

F

8

C

9

D

B

F

0

4

1

5

3

7

0

4

1

5

3

7

8

0

1

4

4

4

4

4

4

4

4

4

4

4

4

1

2

3

rd

rd

rd

rd

0 erd

0 erd

rd

rd

rd

rd

0 erd

0 erd

rd

rd

rd

rd

0 erd

0 erd

rd

rd

rd

rd

0 erd

0 erd

0

rd

rd

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

6

6

6

6

7

7

6

6

6

6

6

6

6

6

6

9

9

F

F

8

8

D

D

B

B

B

B

D

D

D

1 erd

1 erd

1 erd

1 erd

0 erd

0 erd

1 erd

1 erd

8

8

A

A

F

F

F

0

0

0

0

0

0

0

0

0

0

0

0

0 ern

0 ern

0 ern

6

6

disp

disp

B

B

abs

abs

A

A

0

0

abs

abs

disp

disp

2nd byte

3rd byte

4th byte

5th byte

6th byte

7th byte

8th byte

9th byte

10th byte

Size

Instruction

Cannot be used in this LSI