Rev. 1.0, 02/00, page 696 of 1141

REC-CTL Duty Data Register 5 (RCDR5)

1

1

1

1

13

14

15

1

0

3

2

5

4

7

6

9

8

11

10

CMT51

W

12

—

—

—

—

—

—

—

—

0

CMT50

W

0

CMT53

W

0

CMT52

W

0

CMT55

W

0

CMT54

W

0

CMT57

W

0

CMT56

W

0

CMT59

W

0

CMT58

W

0

CMT5B

W

0

CMT5A

W

0

Bit :

Initial value :

R/W :

RCDR5 is a 12-bit write-only register that sets the timing of falling edge of the 0 pulse (short) of

REC-CTL in record or rewrite mode. In detection mode, it is used to detect the long/short pulse.

Only a word access is valid. If a byte access is attempted, correct operation is not guaranteed. If a

read is attempted, an undetermined value is read out. Bits 15 to 12 are reserved, and no write in

them is valid.

It is initialized to H'F000 by a reset, stand-by or module stop.

In record mode, set a value with the 62.5 percent duty cycle obtained from the set time T5

corresponding to the frequency

φ

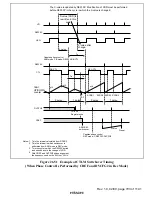

s according to the following equation. See figure 26.60, REC-

CTL Signal Generation Timing.

RCDR5 = T5

×

φ

s/64

φ

is the servo clock frequency (= f

OSC

/2) in Hz, and T5 is the set timing (s).

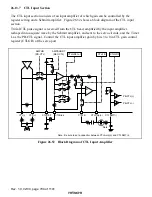

At bit pattern detection, set the 1 pulse long/short threshold value at REV. See figure 26.56, Duty

Discriminator.

RCDR5 = H'FFF

−

(T5'

×

φ

s/80)

φ

s is the servo clock frequency (= f

OSC

/2) in Hz, and T5' is the 1 pulse long/short threshold value at

REV (s).