Rev. 1.0, 02/00, page 573 of 1141

Reference Period Mode Register 2 (RFM2)

0

0

1

1

2

1

3

1

4

1

5

6

7

TBC

R/W

FDS

1

1

1

R/W

Bit :

Initial value :

R/W :

REM2 is an 8-bit read/write register which determines the operational state of the reference signal

generators.

It is initialized to H'FE by a reset and in stand-by and module stop modes. RFM2 is a byte access-

only register; if accessed by a word, correct operation is not guaranteed.

Bit 7

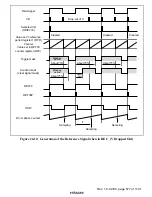

TBC Selection Bit (TBC): Selects whether the reference signal in PB mode is generated

by the VD signal or by the free-run counter.

Bit 7

TBC

Description

0

Generated by the VD signal

1

Generated by the free-run counter

(Initial value)

Bits 6 to 1

Reserved: Cannot be modified and are always read as 1.

Bit 0

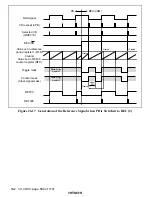

Field Selection Bit (FDS): Determines whether selection between ODD or EVEN is made

for the field signal when PB mode was switched over to REC mode, or these signals are

synchronized with VD signals within a phase error of 90

°

immediately after the switching over.

Bit 0

FDS

Description

0

Generated by the VD signal of ODD or EVEN selected

(Initial value)

1

Generated by the VD signal within mode transition phase error of 90

°