Rev. 1.0, 02/00, page 528 of 1141

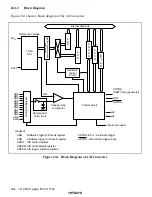

24.4.2

Hardware- or External-Triggered A/D Conversion

The system contains the hardware trigger function that allows to turn on A/D conversion at a

specified timing by use of the hardware trigger (internal signals: ADTRG and DFG) and the

incoming external trigger (

$'75*

). This function can be used to measure an analog signal that

varies in synchronization with an external signal at a fixed timing.

To execute hardware- or external-triggered A/D conversion, select appropriate start factor in

TRGS1 and TRGS0 bits in ADTSR. When the selected triggering occurs, HST flag in ADCSR is

set to 1 and A/D conversion starts. The HST flag remains 1 during A/D conversion, and is

automatically cleared to 0 when conversion ends. For ADTRG start by HSW timing generator in

hardware triggering, see section 26.4, HSW Timing Generator. Setting of the analog input pins on

four channels from AN8 to ANB can be modified with the hardware trigger or the incoming

external trigger. Setting is done from HCH1 and HCH0 bits on ADCR. Pins AN8 to ANB are

also available for software-triggered conversion.

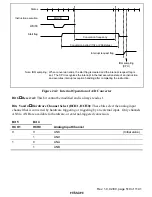

When conversion ends, HEND flag in ADCSR is set to 1. If ADIE bit in ADCSR is also set to 1,

an A/D conversion end interrupt occurs.

If the conversion time or input channel selection in ADCR needs to be changed during A/D

conversion, to avoid malfunctions, first clear the HST flag to 0 to halt A/D conversion.

If software writes 1 in the SST bit to start software-triggered conversion while hardware- or

external-triggered conversion is in progress, the hardware- or external-triggered conversion has

priority and the software-triggered conversion is not executed. At this time, BUSY flag in

ADCSR is set to 1. The BUSY flag is cleared to 0 when the hardware-triggered A/D result

register (AHR) is read.

If conversion is triggered by hardware while software-triggered conversion is in progress, the

software-triggered conversion is immediately canceled and the SST flag is cleared to 0, and SCNL

flag in ADCSR is set to 1 (the SCNL flag is cleared when software writes 1 in the SST bit to start

conversion after the hardware-triggered conversion ends). The analog input channel changes

automatically from the channel that was undergoing software-triggered conversion (selected by

bits SCH3 to SCH0 in ADCR) to the channel selected by bits HCH1 and HCH0 in ADCR for

hardware- or external-triggered conversion. After the hardware- or external-triggered conversion

ends, the channel reverts to the channel selected by the software-triggered conversion channel

select bits in ADCR.

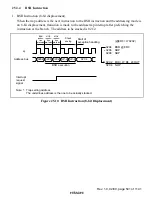

Hardware- or external-triggered conversion has priority over software-triggered conversion, so the

A/D interrupt-handling routine should check the SCNL and BUSY flags when it processes the

converted data.