Rev. 1.0, 02/00, page 319 of 1141

16.2.3

Input Capture Registers A Through D (ICRA Through ICRD)

Input capture register AH to DH (ICRAH to ICRDH)

Input capture register AL to DL (ICRAL to ICRDL)

0

3

0

R

5

0

R

7

0

9

0

R

11

0

13

0

15

R

R

R

0

R

R

1

0

2

0

R

4

0

R

6

0

8

0

R

10

0

12

0

14

ICRA, ICRB, ICRC, ICRD

ICRAH, ICRBH, ICRCH, ICRDH

ICRAL, ICRBL, ICRCL, ICRDL

R

R

R

R

0

R

0

Bit :

Initial value :

R/W :

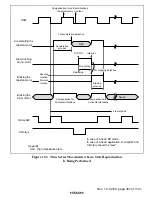

The ICR consists of four 16-bit read-only registers (ICRA through ICRD).

When the falling edge of the input capture input signal is detected, the value is transferred to the

ICRA through ICRD. The ICFA through ICFD of the TCSRX are set to 1 simultaneously. If the

IDIAE through IDIDE of the TCRX are all set to 1, an interrupt request will be issued to the CPU.

The edge of the input signal can be selected by setting the IEDGA through IEDGD of the TCRX.

The ICRC and ICRD can also be used as the buffer register, of the ICRA and ICRB, respectively

by setting the BUFEA and BUFEB of the TCRX to perform buffer operations. Figure 16.2 shows

the connections necessary when using the ICRC as the buffer register of the ICRA. (BUFEA = 1)

When the ICRC is used as the buffer of the ICRA, by setting IEDGA

≠

IEDGC, both of the rising

and falling edges can be designated for use. In case of IEDGA = IEDGC, either one of the rising

edge or the falling edge only is usable. Regarding selection of the input signal edge, see table

16.3.

Note:

Transference from the FRC to the ICR will be performed regardless of the value of the

ICF.