Rev. 1.0, 02/00, page 152 of 1141

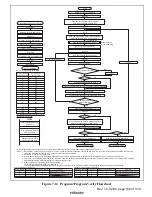

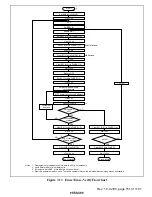

7.5.4

Erase-Verify Mode (n = 1 when the target address range is H'00000 to H'3FFFF

and n = 2 when the target address range is H'40000 to H'47FFF)

In erase-verify mode, data is read after memory has been erased to check whether it has been

correctly erased.

After the elapse of the erase time, erase mode is exited (the En bit in FLMCRn is cleared, then the

ESUn bit is cleared at least 10

µ

s later), the watchdog timer is cleared after the elapse of 10

µ

s or

more, and the operating mode is switched to erase-verify mode by setting the EVn bit in

FLMCRn. Before reading in erase-verify mode, a dummy write of H'FF data should be made to

the addresses to be read. The dummy write should be executed after the elapse of 6.0

µ

s or more.

When the flash memory is read in this state (verify data is read in 16-bit units), the data at the

latched address is read. Wait at least 2

µ

s after the dummy write before performing this read

operation. If the read data has been erased (all 1), a dummy write is performed to the next

address, and erase-verify is performed. If the read data has not been erased, set erase mode again,

and repeat the erase/erase-verify sequence in the same way. However, ensure that the erase/erase-

verify sequence is not repeated more than 100 times. When verification is completed, exit erase-

verify mode, and wait for at least 4

µ

s. If erasure has been completed on all the erase blocks, clear

the SWEn bit in FLMCRn. If there are any unerased blocks, make a 1 bit setting for the flash

memory area to be erased, and repeat the erase/erase-verify sequence in the same way.