Rev. 1.0, 02/00, page 773 of 1141

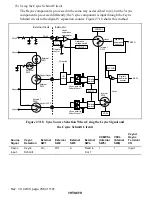

Csync

HVTH

SEPH

HHK

OSCH

HC

Digital H separation

counter

H complement and

mask counter

Forcible HHK

operation

Forcible HHK

operation

Comple-

ment

Comple-

ment

Comple-

ment

Comple-

ment

Comple-

ment

Comple-

ment

Figure 27.7 Timing of HHK Operation

When Complementary Pulses Inserted Three Successive Times While HHKON = 1

27.2.5

Vertical Sync Signal Threshold Register (VVTHR)

0

0

0

0

0

0

0

0

7

W

VVTH0

0

W

VVTH7

6

W

VVTH6

5

W

VVTH5

4

W

VVTH4

3

W

VVTH3

2

W

VVTH2

1

W

VVTH1

Bit :

Initial value :

R/W :

The VVTHR is an 8-bit write-only register for specifying the threshold value for the digital V

separation counter; this value is used to generate the SEPV signal from the Csync signal. The

SEPV signal is set to 1 when the digital V separation counter value matches the VVTHR value

while the Csync is high, and reset to 0 when the digital V separation counter value becomes 00

while the Csync is low. Set the VVTHR value so that the SEPV signal goes high 1/2H or more

after the Vsync start point. When reset, the VVTHR is initialized to H'E0.

Figure 27.8 shows the VVTHR value and the SEPV signal generation timing.

Csync

1/2 H or more

VVTH

H

SEPV

Digital V separation

counter

Figure 27.8 VVTHR Value and SEPV Generation Timing