Rev. 1.0, 02/00, page 387 of 1141

Section 21 Prescalar Unit

21.1

Overview

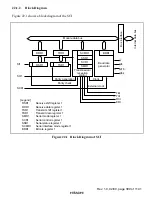

The prescalar unit (PSU) has a 18-bit free running counter (FRC) that uses

φ

as a clock source and

a 5-bit counter that uses

φ

W as a clock source.

21.1.1

Features

•

Prescalar S (PSS)

Generates frequency division clocks that are input to peripheral functions.

•

Prescalar W (PSW)

When a timer A is used as a clock time base, the PSW frequency-divides subclocks and

generates input clocks.

•

Stable oscillation wait time count

During the return from the low power consumption mode excluding the sleep mode, the FRC

counts the stable oscillation wait time.

•

8-bit PWM

The lower 8 bits of the FRC is used as 8-bit PWM cycle and duty cycle generation counters.

(Conversion cycle: 256 states)

•

8-bit input capture by

,&

pins

Catches the 8 bits of 2

15

to 2

8

of the FRC according to the edge of the

,&

pin for remote control

receiving.

•

Frequency division clock output

Can output the frequency division clock for the system clock or the frequency division clock

for the subclock from the frequency division clock output pin (TMOW).