Rev. 1.0, 02/00, page 1049 of 1141

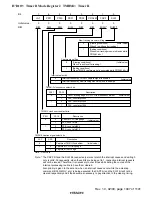

H'D11F: Timer R Control/Status Register TMRCS: Timer R

0

1

1

1

2

0

R/(W)*

3

0

4

0

R/(W)*

5

0

6

0

7

R/(W)*

R/W

TMRI1E

R/W

TMRI2E

0

R/W

TMRI3E

TMRI3

TMRI2

TMRI1

Note: * Only 0 can be written to clear the flag.

TMRI3 interrupt request is disabled

(Initial value)

TMRI3 interrupt request is enabled

0

1

TMRI3 interrupt enable bit

TMRI2 interrupt request is disabled

(Initial value)

TMRI2 interrupt request is enabled

0

1

TMRI2 interrupt enable bit

TMRI1 interrupt request is disabled

(Initial value)

TMRI1 interrupt request is enabled

0

1

TMRI1 interrupt enable bit

TMRI1 interrupt request flag

[Clearing conditions]

(Initial value)

When 0 is written after reading 1

[Setting conditions]

When TMRU-1 underflows

0

1

TMRI2 interrupt request flag

[Clearing conditions]

(Initial value)

When 0 is written after reading 1

[Setting conditions]

When TMRU-2 underflows or when capstan motor

acceleration/deceleration operation ends

0

1

TMRI3 interrupt request flag

[Clearing conditions]

(Initial value)

When 0 is written after reading 1

[Setting conditions]

When interrupt source selected at CP/SLM bit in

TMRM2 is generated

0

1

Initial value :

—

—

—

—

Bit

R/W

:

: