Rev. 1.0, 02/00, page 772 of 1141

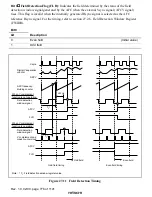

Csync

HVTH

SEPH

HHK

OSCH

HC

Digital H separation

counter

Hsync-Vsync

phase-difference

error

Pulse

lost

H complement

and mask counter

Comple-

ment

Comple-

ment

Figure 27.5 Timing of Hsync-Vsync Phase-Difference Error

When Equalizing Pulse Lost at Hsync Pulse Position

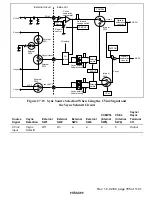

Note:

When 2.35-

µ

s equalizing pulses are eliminated, the complement function operates for the

eliminated period. Accordingly, the rising edge of the Vsync signal for the even field is

detected as an Hsync pulse. Therefore, to not generate an Hsync pulse at this position, set

the HHKON bit (bit 2) of the SEPCR to 1 so that the HHK function is forcibly operated

when complementary pulses are inserted three successive times. Figures 27.6 and 27.7

show this timing.

Csync

HVTH

SEPH

HHK

OSCH

HC

Digital H separation

counter

Comple-

ment

Comple-

ment

Comple-

ment

Comple-

ment

Phase-difference

error

H complement and

mask counter

Comple-

ment

Comple-

ment

Comple-

ment

Figure 27.6 Timing of Hsync-Vsync Phase-Difference Error

When Equalizing Pulse Not Detected