Rev. 1.0, 02/00, page 607 of 1141

•

Loop Mode

The data output cycle is repeated from stage 0 to the final stage selected in the HSW loop

number setting register. As in single mode, the output pattern data is output when the timing

pattern matches the counter value. In loop mode, the FIFO data is retained.

Data in each FIFO group can be modified in loop mode. The FIFO group currently outputting

data can be checked by the OFG bit of the HSW mode register 2; after checking the outputting

FIFO group, clear the FIFO group which is not outputting data, then write new data to it.

Writing new data must be completed before the FIFO group starts operation. The FIFO cannot

be modified partially because the write pointer is outside the loop stages.

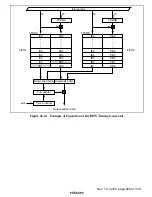

Figures 26.23 and 26.24 show examples of the timing waveform and operation of the HSW timing

generator.