Rev. 1.0, 02/00, page 1002 of 1141

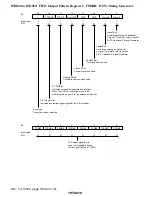

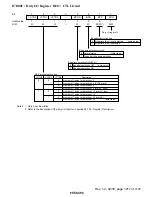

H'D061: HSW Mode Register 2 HSM2: HSW Timing Generator

0

0

1

0

R

2

0

R/W

3

0

4

0

R/W

0

R/W

5

6

0

7

EDG

ISEL1

SOFG

OFG

VFF/NFF

0

R/W

FRT

R/W

R/W

R/W

FGR20FF

LOP

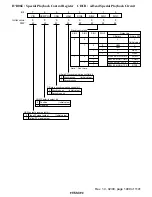

Free-run bit

0 5-bit DFG counter and 16-bit timer counter

(Initial value)

1 16-bit FRC

FRG2 clear stop bit

0 16-bit timer counter clearing by DFG reference register 2 is enabled

(Initial value)

1 16-bit timer counter clearing by DFG reference register 2 is disabled

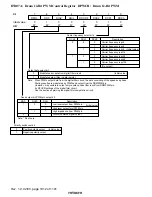

Mode select bit

0 Signal mode

(Initial value)

1 Loop mode

DFG edge select bit

0 Calculated by DFG rising edge

(Initial value)

1 Calculated by DFG falling edge

Interrupt select bit

0 Interrupt request is generated by rising of FIFO STRIG signal

(Initial value)

1 Interrupt request is generated by FIFO match signal

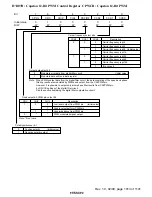

FIFO output group select bit

0 20-stage output by FIFO1 and FIFO2

(Initial value)

1 10-stage output by FIFO1 only

Output FIFO group flag

0 Outputting pattern by FIFO1 (Initial value)

1 Outputting pattern by FIFO2

VideoFF/NallowFF output switchover bit

0 VideoFF output

(Initial value)

1 NarrowFF output

Bit :

Initial value :

R/W :