Rev. 1.0, 02/00, page 926 of 1141

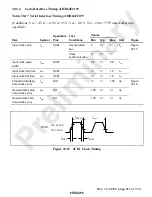

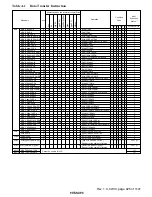

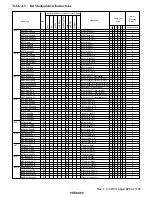

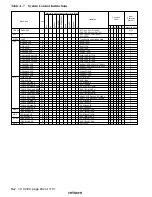

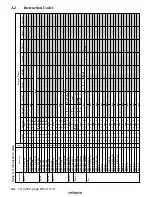

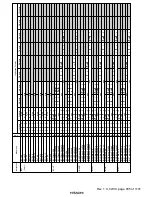

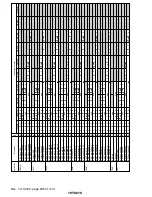

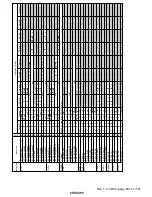

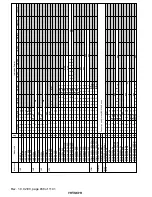

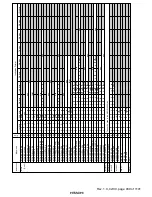

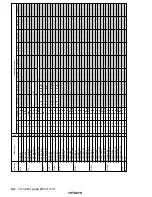

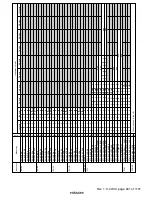

Table A.2

Arithmetic Instructions

ADD.B #xx:8,Rd

ADD.B Rs,Rd

ADD.W #xx:16,Rd

ADD.W Rs,Rd

ADD.L #xx:32,ERd

ADD.L ERs,ERd

ADDX #xx:8,Rd

ADDX Rs,Rd

ADDS #1,ERd

ADDS #2,ERd

ADDS #4,ERd

INC.B Rd

INC.W #1,Rd

INC.W #2,Rd

INC.L #1,ERd

INC.L #2,ERd

DAA Rd

SUB.B Rs,Rd

SUB.W #xx:16,Rd

SUB.W Rs,Rd

SUB.L #xx:32,ERd

SUB.L ERs,ERd

SUBX #xx:8,Rd

SUBX Rs,Rd

SUBS #1,ERd

SUBS #2,ERd

SUBS #4,ERd

DEC.B Rd

DEC.W #1,Rd

DEC.W #2,Rd

DEC.L #1,ERd

DEC.L #2,ERd

DAS Rd

MULXU.B Rs,Rd

MULXU.W Rs,ERd

MULXS.B Rs,Rd

MULXS.W Rs,ERd

DIVXU.B Rs,Rd

DIVXU.W Rs,ERd

DIVXS.B Rs,Rd

DIVXS.W Rs,ERd

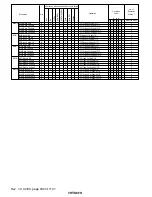

CMP.B #xx:8,Rd

CMP.B Rs,Rd

CMP.W #xx:16,Rd

CMP.W Rs,Rd

CMP.L #xx:32,ERd

CMP.L ERs,ERd

NEG.B Rd

NEG.W Rd

NEG.L ERd

EXTU.W Rd

EXTU.L ERd

EXTS.W Rd

EXTS.L ERd

TAS @ERd

MAC @ERn+,@ERm+

CLRMAC

LDMAC ERs,MACH

LDMAC ERs,MACL

STMAC MACH,ERd

STMAC MACL,ERd

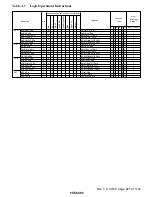

B

B

W

W

L

L

B

B

L

L

L

B

W

W

L

L

B

B

W

W

L

L

B

B

L

L

L

B

W

W

L

L

B

B

W

B

W

B

W

B

W

B

B

W

W

L

L

B

W

L

W

L

W

L

B

2

4

6

2

4

6

2

2

4

6

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

4

4

2

2

4

4

2

2

2

2

2

2

2

2

2

2

ADD

ADDX

ADDS

INC

DAA

SUB

SUBX

SUBS

DEC

DAS

MULXU

MULXS

DIVXU

DIVXS

CMP

NEG

EXTU

EXTS

TAS

MAC

CLRMAC

LDMAC

STMAC

Mnemonic

Size

#xx

Rn

@ERn

@(d,ERn)

@-ERn/@ERn+

@aa

@(d,PC)

@@aa

—

Rd8+#xx:8

→

Rd8

Rd8+Rs8

→

Rd8

Rd16+#xx:16

→

Rd16

Rd16+Rs16

→

Rd16

ERd32+#xx:32

→

ERd32

ERd32+ERs32

→

ERd32

Rd8+#xx:8+C

→

Rd8

Rd8+Rs8+C

→

Rd8

ERd32+1

→

ERd32

ERd32+2

→

ERd32

ERd32+4

→

ERd32

Rd8+1

→

Rd8

Rd16+1

→

Rd16

Rd16+2

→

Rd16

ERd32+1

→

ERd32

ERd32+2

→

ERd32

Rd8 10 Decimal adjust

→

Rd8

Rd8-Rs8

→

Rd8

Rd16-#xx:16

→

Rd16

Rd16-Rs16

→

Rd16

ERd32-#xx:32

→

ERd32

ERd32-ERs32

→

ERd32

Rd8-#xx:8-C

→

Rd8

Rd8-Rs8-C

→

Rd8

ERd32-1

→

ERd32

ERd32-2

→

ERd32

ERd32-4

→

ERd32

Rd8-1

→

Rd8

Rd16-1

→

Rd16

Rd16-2

→

Rd16

ERd32-1

→

ERd32

ERd32-2

→

ERd32

Rd8 10 Decimal adjust

→

Rd8

Rd8

×

Rs8

→

Rd16(Multiplication w/o sign)

Rd16

×

Rs16

→

ERd32

(Multiplication w/o sign)

Rd8

×

Rs8

→

Rd16(Multiplication w/o sign)

Rd16

×

Rs16

→

ERd32

(Multiplication w/o sign)

Rd16

÷

Rs8

→

Rd16 (RdH: Remainder, RdL:

Quatient)(Division w/o sign)

ERd32

÷

Rs16

→

ERd32 (Ed:Remainder,

Rd: Quatient)(Division with sign)

Rd16

÷

Rs8

→

Rd16(RdH: Remainder, RdL:

Quatient)(Division w/o sign)

ERd32

÷

Rs16

→

ERd32 (Ed:Remainder,

Rd: Quatient)(Division with sign)

Rd8-#xx:8

Rd8-Rs8

Rd16-#xx:16

Rd16-Rs16

ERd32-#xx:32

ERd32-ERs32

0-Rd8

→

Rd8

0-Rd16

→

Rd16

0-ERd32

→

ERd32

0

→

(<Bits 15 to 8> of Rd16)

0

→

(<Bits 31 to 16> of ERd32)

(<Bit7> of Rd16)

→

(<Bits 15 to 8> of Rd16)

(<Bit15> of ERd32)

→

(<Bits31 to 16> of ERd32)

@ERd-0

→

CCR set, (1)

→

(<Bit7> of @ERd)

Operation

Condition

Code

I

H N Z V C

Advanced Mode

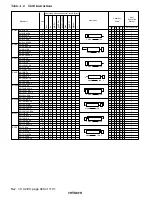

4

—

—

—

*

1

1

2

1

3

1

1

1

1

1

1

1

1

1

1

1

1

1

2

1

3

1

1

1

1

1

1

1

1

1

1

1

1

12

20

13

21

12

20

13

21

1

1

2

1

3

1

1

1

1

1

1

1

1

4

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

[3]

[3]

[4]

[4]

—

—

—

—

—

—

—

—

*

[3]

[3]

[4]

[4]

—

—

—

—

—

—

—

—

*

—

—

—

—

—

—

—

—

[3]

[3]

[4]

[4]

—

—

—

—

—

—

—

—

—

—

—

—

—

[6]

[6]

[8]

[8]

0

0

[5]

[5]

—

—

—

[5]

[5]

—

—

—

—

—

[7]

[7]

[7]

[7]

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

*

—

—

—

—

—

—

—

—

0

0

0

0

0

—

—

—

—

—

Cannot be used in this LSI

[2]

Addressing Mode and Instruction Length (Bytes)

No of

Execution

States

*1