Rev. 1.0, 02/00, page 173 of 1141

Section 9 Clock Pulse Generator

9.1

Overview

This LSI has a built-in clock pulse generator (CPG) that generates the system clock (

φ

), the bus

master clock, and internal clocks.

The clock pulse generator consists of a system clock oscillator, a duty adjustment circuit, clock

selection circuit, medium-speed clock divider, subclock oscillator, and subclock division circuit.

9.1.1

Block Diagram

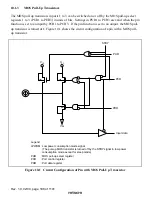

Figure 9.1 shows a block diagram of the clock pulse generator.

System

clock

oscillator

Duty

adjustment

circuit

Clock

selection

circuit

Medium-

speed clock

divider

Subclock

oscillator

Subclock

division

circuit

OSC1

OSC2

X1

X2

φ

/16,

φ

/32,

φ

/64

φ

w/2,

φ

w/4,

φ

w/8

φ

SUB

φ

or

φ

SUB

Timer A

count clock

Internal clock

To supporting modules

Bus master clock

To CPU

φ

SUB (

φ

w/2,

φ

w/4,

φ

w/8)

Figure 9.1 Block Diagram of Clock Pulse Generator

9.1.2

Register Configuration

The clock pulse generator is controlled by SBYCR and LPWRCR. Table 9.1 shows the register

configuration.

Table 9.1

CPG Registers

Name

Abbreviation

R/W

Initial Value

Address

*

Standby control register

SBYCR

R/W

H'00

H'FFEA

Low-power control register

LPWRCR

R/W

H'00

H'FFEB

Note:

*

Lower 16 bits of the address.