Rev. 1.0, 02/00, page 741 of 1141

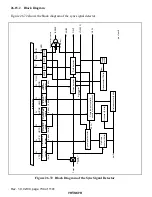

Sync Signal Control Register (SYNCR)

0

0

1

0

R

2

0

R/(W)*

3

1

4

5

6

1

7

—

—

—

—

—

—

—

—

R/W

R/W

NIS/VD

NOIS

FLD

SYCT

1

1

1

Note: * Only 0 can be written

Bit :

Initial value :

R/W :

SYNCR is an 8-bit register that controls the noise detection, field detection, polarity of the sync

signal input, etc.

It is initialized to H'F8 by a reset, or in stand-by mode. Bits 7 to 4 are reserved. No write is valid.

Bit 1 is read-only.

Bits 7 to 4

Reserved: Cannot be modified and are always read as 1.

Bit 3

Interrupt Selection Bit (NIS/VD): Selects whether an interrupt request is generated by

noise level detection or VD signal detection.

Bit 3

NIS/VD

Description

0

Interrupt at the noise level

1

Interrupt at VD

(Initial value)

Bit 2

Noise Detection Flag (NOIS): NOIS is a status flag indicating that the noise counts

reached at more than four times of the value set in NDR. The flag is cleared only by writing 0

after reading 1. Care is required because it is not cleared automatically.

Bit 2

NOIS

Description

0

Noise count is smaller than four times of the value set in NDR

(Initial value)

1

Noise count is the same or greater than four times of the value set in NDR