Rev. 1.0, 02/00, page 1083 of 1141

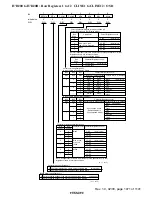

H'D240: Sync Separation Input Mode Register SEPIMR: Sync Separator

0

0

1

0

R/W

2

0

R/W

3

0

4

5

6

0

7

R/W

R/W

VSEL

CCMPV1

R/W

R/W

CCMPV0

R/W

CCMPSL

R/W

SYNCT

DLPFON

—

FRQSEL

0

0

0

Digital LPF control

0

1

Reference clock frequency select

0

1

Vsync input signal select

0

1

Csync separation comparator input select

0

1

0

(Initial value)

1

Sync signal polarity select

:

:

:

Csync separation comparator slicing voltage select

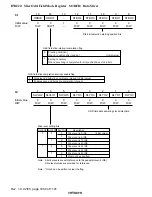

Description

0

0

CCMPV1

CCMPV0

1

0

1

1

Bit

Initial value

R/W

The Csync slicing level is 10 IRE (Initial value)

The Csync slicing level is 5 IRE

The Csync slicing level is 15 IRE

The Csync slicing level is 20 IRE

The Csync separation comparator input is selected

The Csync/Hsync terminal operates as an output terminal (Initial value)

The Csync Schmitt input is selected

The Csync/Hsync terminal operates as an input terminal

Vsync Schmitt input (Initial value)

Csync Schmitt input

The digital LPF does not operate (Initial value)

The digital LPF operates

576 times the horizontal sync frequency

(Initial value)

448 times the horizontal sync frequency