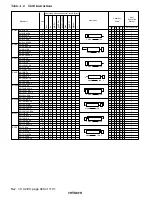

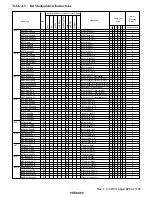

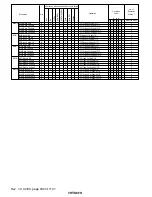

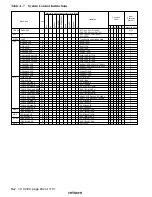

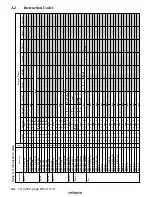

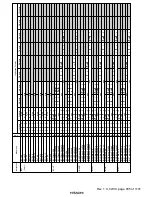

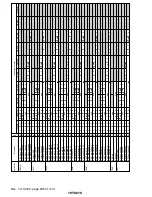

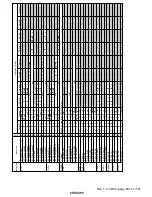

Rev. 1.0, 02/00, page 942 of 1141

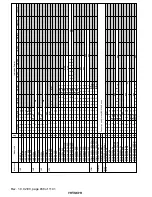

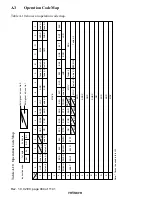

SUB

SUBS

SUBX

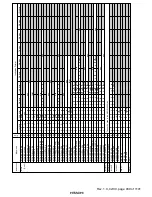

TAS

TRAPA

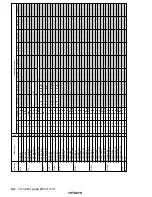

XOR

XORC

SUB.B Rs,Rd

SUB.W #xx:16,Rd

SUB.W Rs,Rd

SUB.L #xx:32,ERd

SUB.L ERs,ERd

SUBS #1,ERd

SUBS #2,ERd

SUBS #4,ERd

SUBX #xx:8,Rd

SUBX Rs,Rd

TAS @ERd

TRAPA #x:2

XOR.B #xx:8,Rd

XOR.B Rs,Rd

XOR.W #xx:16,Rd

XOR.W Rs,Rd

XOR.L #xx:32,ERd

XOR.L ERs,ERd

XORC #xx:8,CCR

XORC #xx:8,EXR

Mnemonic

Instruction Format

1st byte

B

W

W

L

L

L

L

L

B

B

B

—

B

B

W

W

L

L

B

B

1

7

1

7

1

1

1

1

B

1

0

5

D

1

7

6

7

0

0

0

8

9

9

A

A

B

B

B

rd

E

1

7

rd

5

9

5

A

1

5

1

rs

3

rs

3

1 ers

0

8

9

IMM

rs

E

IMM

IMM

rs

5

rs

5

F

IMM

4

rd

rd

rd

0 erd

0 erd

0 erd

0 erd

0 erd

rd

0

0

rd

rd

rd

0 erd

0

1

7

6

0

IMM

B

IMM

5

5

0 erd

0 ers

IMM

IMM

C

IMM

0 erd

2nd byte

3rd byte

4th byte

5th byte

6th byte

7th byte

8th byte

9th byte

10th byte

Size

Instruction

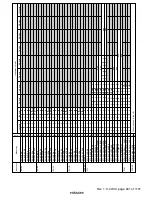

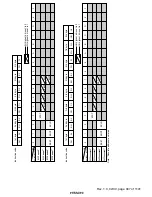

Notes: *

Either 1 or 0 can be set to bit 7 in 4th byte of MOV.L Ers, @(d: 32, Erd) instruction.

IMM

: Immediate data (2, 3, 8, 16, 32 bits)

abs

: Absolute address (8, 16, 24, 32 bits)

disp

: Displacement (8, 16, 32 bits)

rs, rd, rn

: Register fields (8-bit register or 16-bit register is selected in 4 bits. rs, rd and rn correspond to the operand t

ype Rs, Rd, and Rn respectively.)

ers, erd, ern, erm

: Register fields (address register or 32-bit register is selected in 3 bits. ers, erd ern and erm correspond

to the operand type ERs,

ERd, ERn and Rm respectively.)

00