Rev. 1.0, 02/00, page 527 of 1141

24.4

Operation

The A/D converter operates by successive approximations with 10-bit resolution.

24.4.1

Software-Triggered A/D Conversion

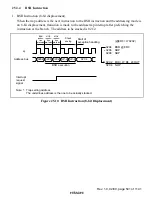

A/D conversion starts when software sets the software A/D start flag (SST bit) to 1. The SST bit

remains set to 1 during A/D conversion, and is automatically cleared to 0 when conversion ends.

Conversion can be software-triggered on any of the 12 channels provided by analog input pins

AN0 to ANB. Bits SCH3 to SCH0 in ADCR select the analog input pin used for software-

triggered A/D conversion. Pins AN8 to ANB are also available for hardware- or external-

triggered conversion.

When conversion ends, SEND flag in ADCSR bit is set to 1. If ADIE bit in ADCSR is also set to

1, an A/D conversion end interrupt occurs.

If the conversion time or input channel selection in ADCR needs to be changed during A/D

conversion, to avoid malfunctions, first clear the SST bit to 0 to halt A/D conversion.

If software writes 1 in the SST bit to start software-triggered conversion while hardware- or

external-triggered conversion is in progress, the hardware- or external-triggered conversion has

priority and the software-triggered conversion is not executed. At this time, BUSY flag in

ADCSR is set to 1. The BUSY flag is cleared to 0 when the hardware-triggered A/D result

register (AHR) is read. If conversion is triggered by hardware while software-triggered

conversion is in progress, the software-triggered conversion is immediately canceled and the SST

flag is cleared to 0, and SCNL flag in ADCSR is set to 1. The SCNL flag is cleared when

software writes 1 in the SST bit to start conversion after the hardware-triggered conversion ends.