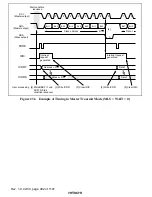

Rev. 1.0, 02/00, page 492 of 1141

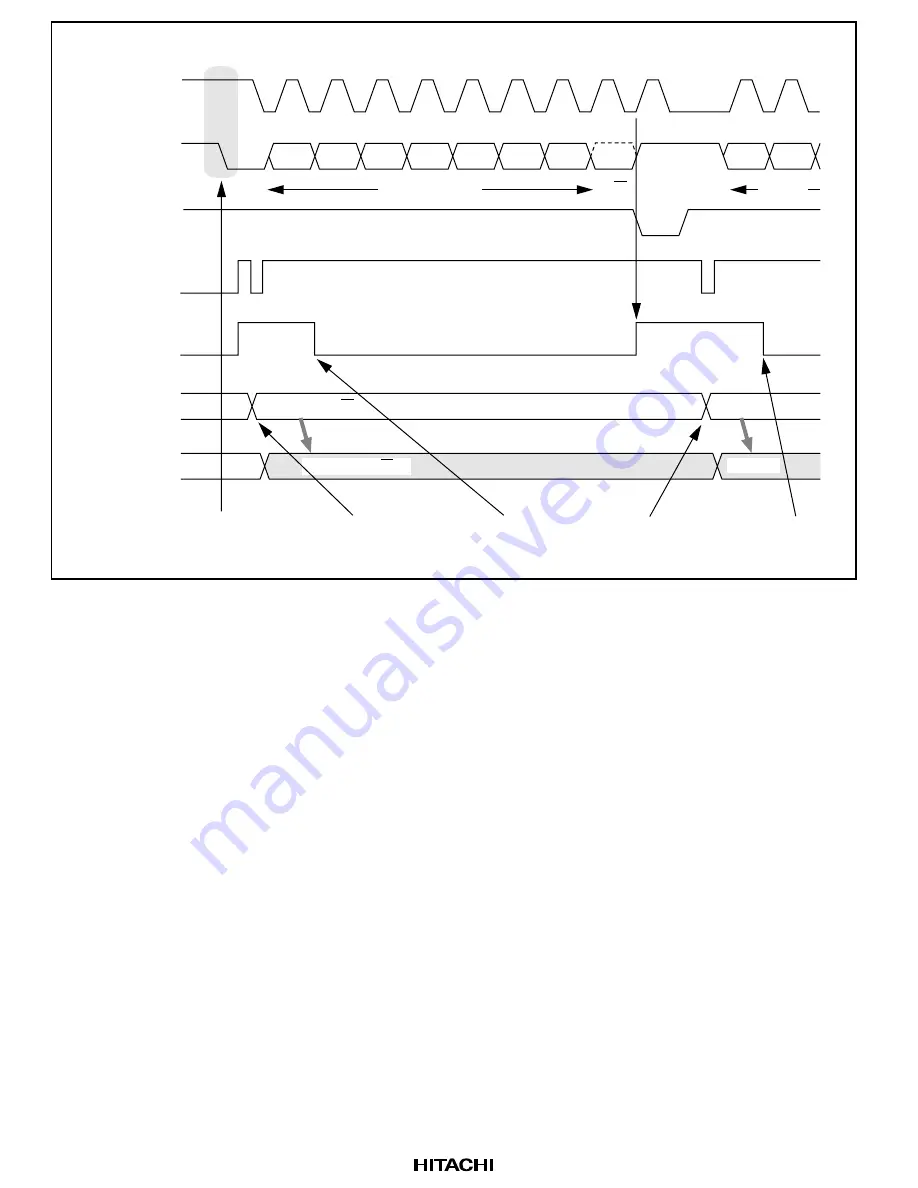

SDA

(Master output)

SDA

(Slave output)

2

1

2

1

4

3

6

5

8

7

9

Bit 7

Bit 6

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

IRIC

ICDRT

ICDRS

TDRE

SCL

(Master output)

Start condition

issuance

Interrupt

request

generated

Interrupt request

generated

Data 1

A RW

Data 1

A RW

Write BBSY=1 and

SCP=0 (Start

condition issuance)

User processing

Slave address

Data 1

R/W

[4]

A

[2]

Write ICDR

[3]

Clear IRIC

[3]

Write ICDR

[5]

Clear IRIC

[5]

Figure 23.6 Example of Timing in Master Transmit Mode (MLS = WAIT = 0)