Rev. 1.0, 02/00, page 519 of 1141

Conversion frequency

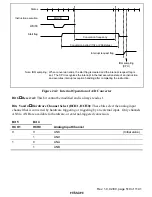

Note: IRQ sampling;

Conversion period (134 or 266 states)

Interrupt request flag

IRQ sampling

(CPU)

States

Instruction execution

MOV.B

WRITE

Start flag

When conversion ends, the start flag is cleared and the interrupt request flag is

set. The CPU recognizes the interrupt in the last execution state of an instruction,

and executes interrupt exception handling after completing the instruction.

Figure 24.2 Internal Operation of A/D Converter

Bit 6

Reserved: This bit cannot be modified and is always read as 1.

Bits 5 and 4

Hardware Channel Select (HCH1, HCH0): These bits select the analog input

channel that is converted by hardware triggering or triggering by an external input. Only channels

AN8 to ANB are available for hardware- or external-triggered conversion.

Bit 5

Bit 4

HCH1

HCH0

Analog Input Channel

0

AN8

(Initial value)

0

1

AN9

0

ANA

1

1

ANB