Rev. 1.0, 02/00, page 179 of 1141

External Clock: The external clock signal should have the same frequency as the system clock

(

φ

).

Table 9.3 and figure 9.6 show the input conditions for the external clock.

Table 9.3

External Clock Input Conditions

V

CC

= 4.0 to 5.5 V

Item

Symbol

Min

Max

Unit

Test Conditions

External clock input low

pulse width

t

EXL

40

ns

External clock input high

pulse width

t

EXH

40

ns

External clock rise time

t

EXr

10

ns

External clock fall time

t

EXf

10

ns

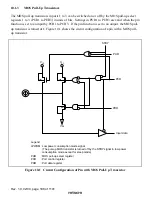

Figure 9.6

t

EXH

t

EXL

t

EXr

t

EXf

OSC1

Figure 9.6 External Clock Input Timing

Table 9.4 shows the external clock output settling delay time, and figure 9.7 shows the external

clock output settling delay timing. The oscillator and duty adjustment circuit have a function for

adjusting the waveform of the external clock input at the OSC1 pin. When the prescribed clock

signal is input at the OSC1 pin, internal clock signal output is fixed after the elapse of the external

clock output settling delay time (t

DEXT

). As the clock signal output is not fixed during the t

DEXT

period, the reset signal should be driven low to maintain the reset state.