Rev. 1.0, 02/00, page 545 of 1141

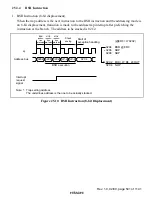

2. JMP Instruction (Memory indirect)

When the trap address is the next instruction to the JMP instruction and the addressing mode is

memory indirect, transition is made to the address trap interrupt after prefetching the

instruction at the branch. The address to be stacked is 02E4.

φ

Address bus

Interrupt

request

signal

JMP execution

Start of

exception

handling

0294

006C 02E4

006C

0296

006E

02E6

0294 JMP @@H'6C:8

0296 NOP

0298 NOP

02E4 NOP

02E6 NOP

: :

006C H'02E4

: :

*

Data

fetch

Internal

opera-

tion

JMP

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

Note:

*

Trap setting address

The underlines address is the one to be actually stacked.

Figure 25.14 JMP Instruction (Memory Indirect)

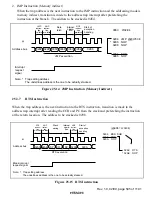

25.3.7

RTS Instruction

When the trap address is the next instruction to the RTS instruction, transition is made to the

address trap interrupt after reading the CCR and PC from the stack and prefetching the instruction

at the return location. The address to be stacked is 0298.

φ

Address bus

Break interrupt

request signal

RTS execution

Start of

exception

handling

02AC

SP

0298

SP

02AE

SP+2

029A

Stack

saving

0296 BSR SUB

0298 NOP

029A NOP

02AC RTS

(@ER0 = H'02C8)

02AE NOP

*

: :

Internal

opera-

tion

RTS

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

NOP

instruc-

tion

pre-fetch

Note:

*

Trap setting address

The underlines address is the one to be actually stacked.

Figure 25.15 RTS Instruction